## Advanced Micro Devices

# The Am2900 Family Data Book

Copyright 1976 by Advanced Micro Devices, Inc. 901 Thompson Place, Sunnyvale, California 94086 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

#### **TABLE OF CONTENTS**

| Introduction              |                                                                |

|---------------------------|----------------------------------------------------------------|

| The Am2900 Fami           |                                                                |

| Am2901                    | Four-Bit Bipolar Microprocessor Slice                          |

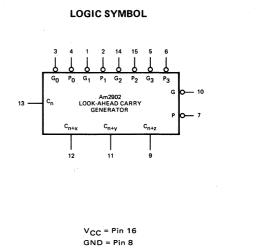

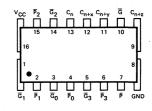

| Am2902                    | High-Speed Look-Ahead Carry Generator                          |

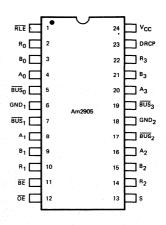

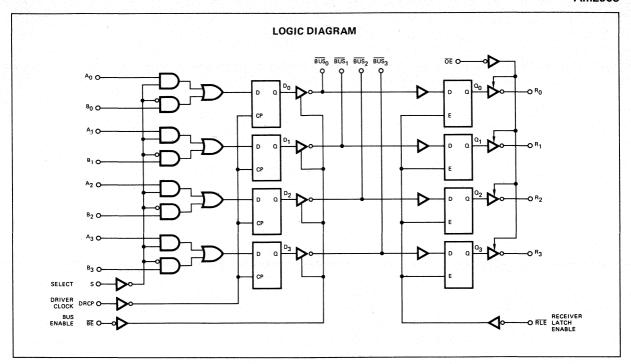

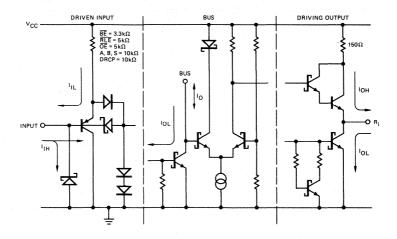

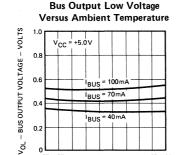

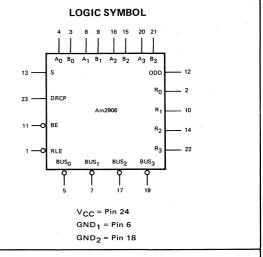

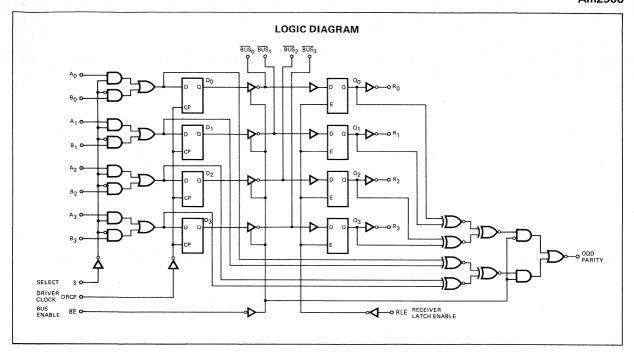

| Am2905                    | Quad Two-Input OC Bus Transceiver With Three-State Receiver 26 |

| Am2906                    | Quad Two-Input OC Bus Transceiver With Parity                  |

| Am2907                    | Quad Bus Transceiver With Three-State Receiver And Parity      |

| Am2909                    | Microprogram Sequencer                                         |

| Am2911                    | Microprogram Sequencer                                         |

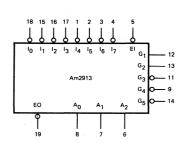

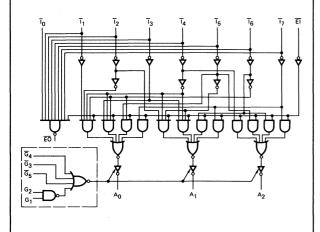

| Am2913                    | Priority Interrupt Expander                                    |

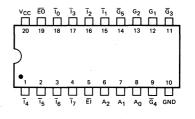

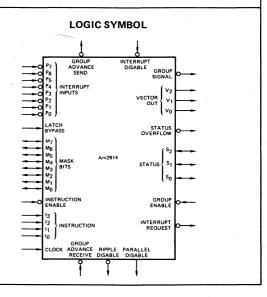

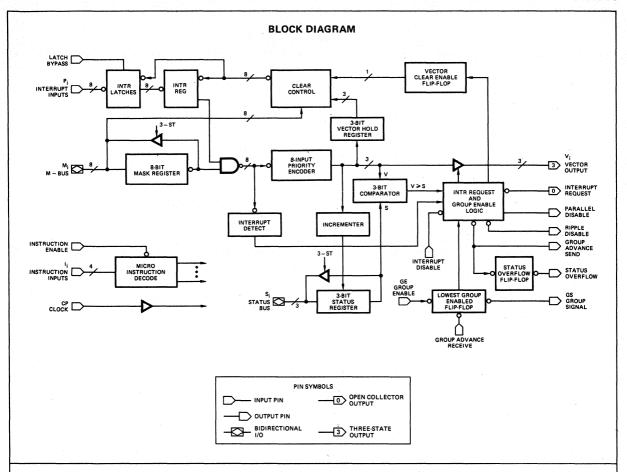

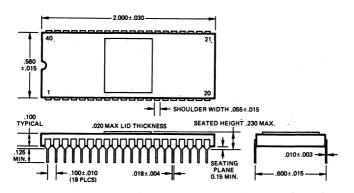

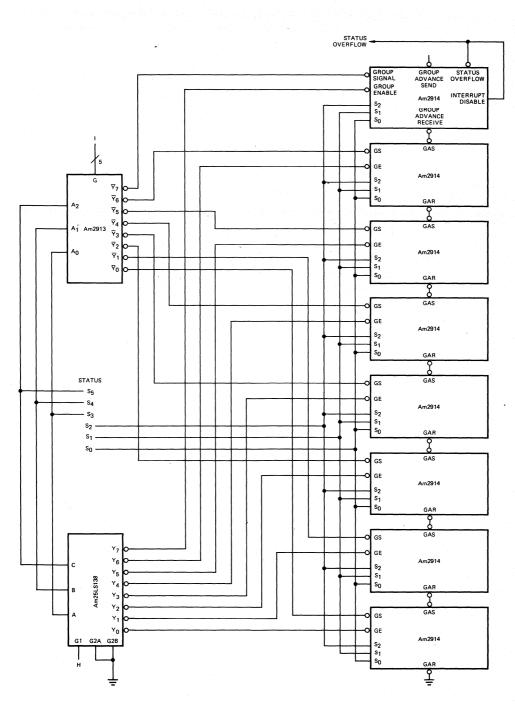

| Am2914                    | Vectored Priority Interrupt Encoder                            |

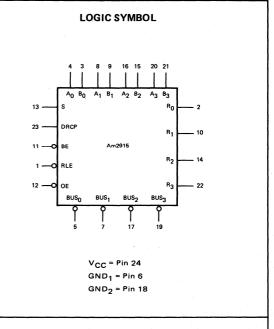

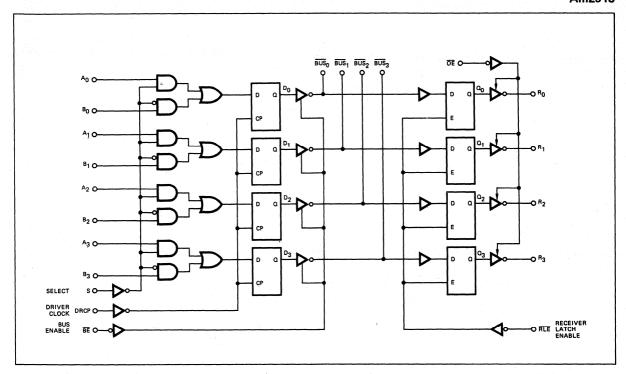

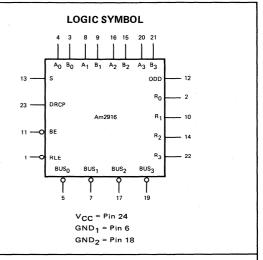

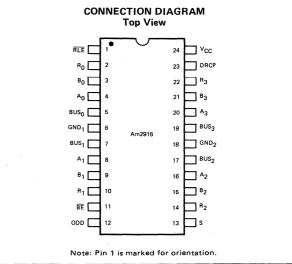

| Am2915                    | Quad Three-State Bus Transceiver With Interface Logic          |

| Am2916                    | Quad Three-State Bus Transceiver With Interface Logic 80       |

| Am2917                    | Quad Three-State Bus Transceiver With Interface Logic          |

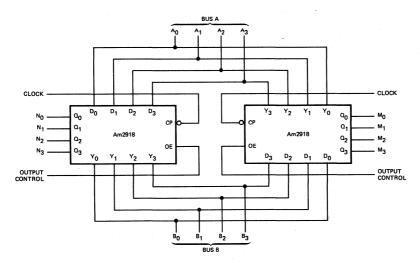

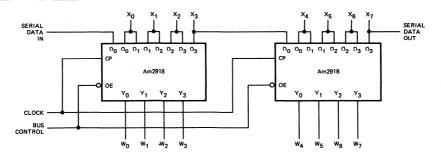

| Am2918                    | Quad D Register With Standard And Three-State Outputs 92       |

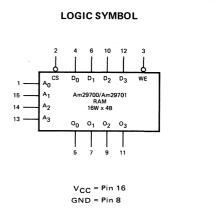

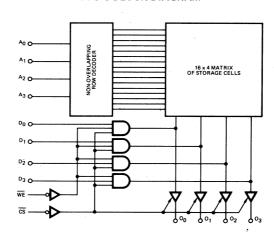

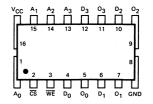

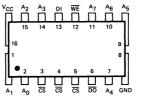

| Am29700/701               | Non-Inverting 64-Bit Random Access Memory                      |

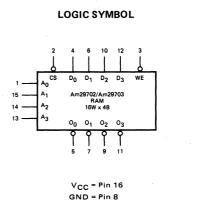

| Am29702/703               | Inverting 64-Bit Random Access Memories                        |

| Am29704/705               | 16-Word By 4-Bit Two-Port RAM                                  |

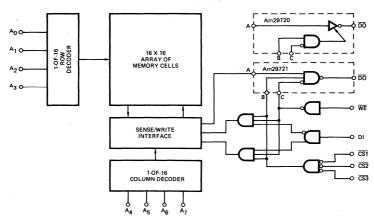

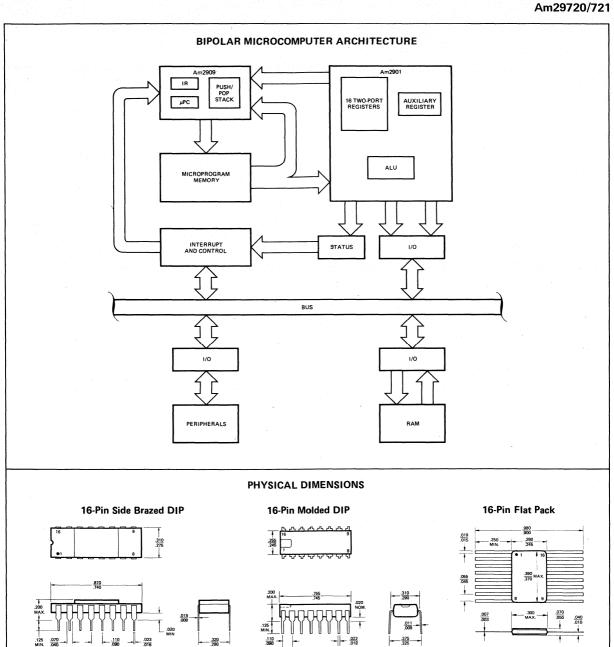

| Am29720/721               | Low-Power Schottky 256-Bit Random Access Memories              |

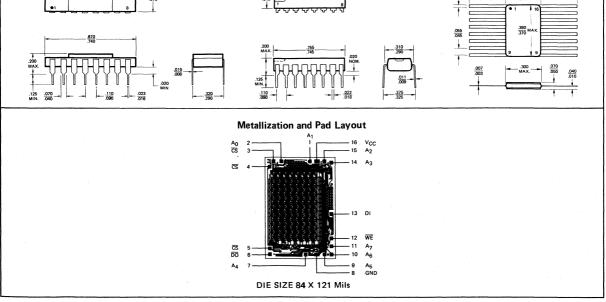

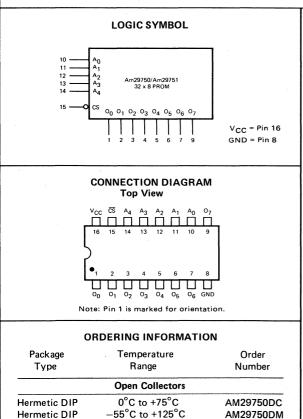

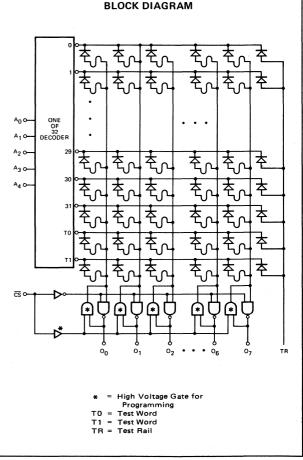

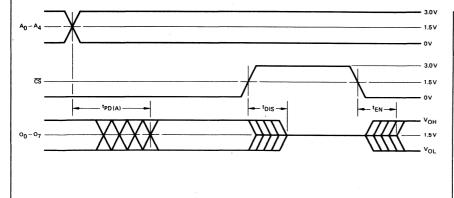

| Am29750/751               | 32-Word By 8-Bit PROM's                                        |

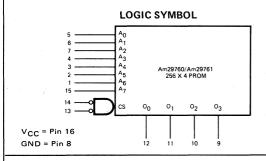

| Am29760/761               | 256-Word By 4-Bit PROM's                                       |

| Am29790/791               | Field Programmable Logic Array                                 |

| <b>Application Notes:</b> |                                                                |

| A Computer Co             | ntrol Unit Using The Am2909                                    |

| Kits:                     |                                                                |

| Am2900K1                  |                                                                |

| Schottky and Low-         | Power Schottky Circuits                                        |

|                           | 1                                                              |

|                           |                                                                |

|                           | istributors                                                    |

#### LIST OF CHANGES

Listed below are changes incorporated in this data book relative to earlier editions of these data sheets. Am2901

- 1. RO/LI and LO/RI dropped from shift pins. The shift pins are renamed RAM0, RAM3, Q0, and Q3.

- 2. All references to left and right eliminated.

- 3. Figure 4 revised for clarity.

- 4. Figure 8, line 7 corrected.

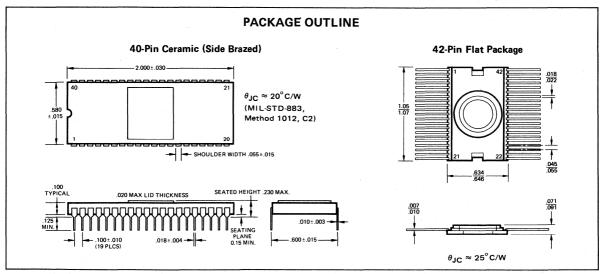

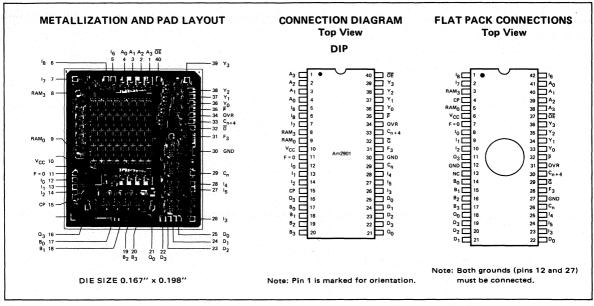

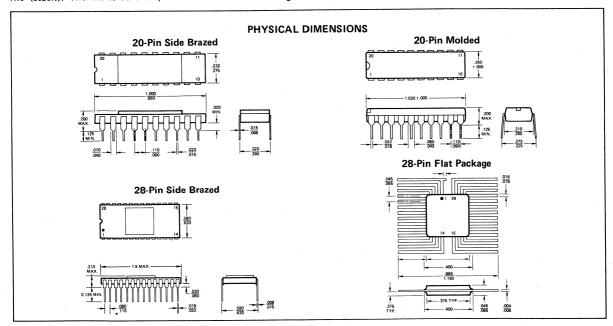

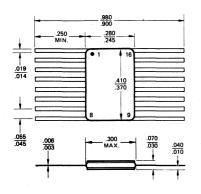

- 5. Flat pack dimensions and pin-out added.

- 6. G added to VOH spec at -1.6mA IOH.

- 7. Delays from D inputs in logic mode added to Table II.

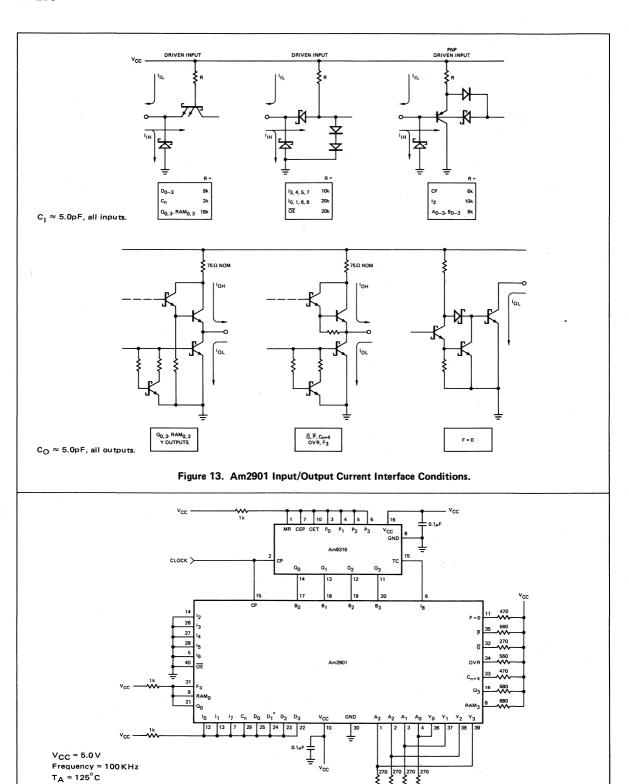

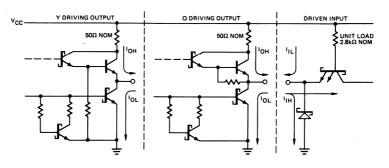

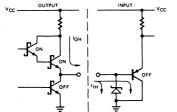

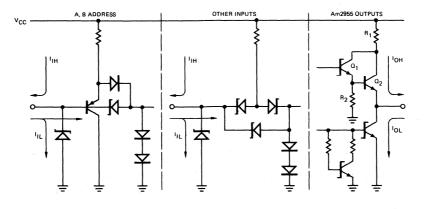

- 8. Input/output circuits added.

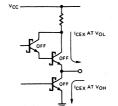

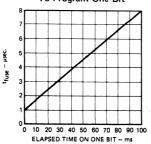

- 9. Burn-in diagram added.

#### Am2905

1. AC data specified over operating range.

#### Am2906

1. AC data specified over operating range.

#### Am2907

1. AC data specified over operating range.

#### Am2909

1. AC data specified over operating range.

#### Am2911

1. New data sheet. Added to Am2909 data sheet.

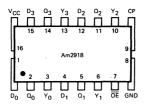

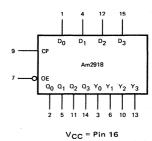

#### Am2918

1. I<sub>CC</sub> max. lowered from 130mA to 120mA.

#### Am29720/721

1. Part number changed from Am2950/51.

#### Am29760/761

1. Part number changed from Am2970/71

#### Am29790/791

1. Part number changed from Am2980/81.

#### INTRODUCTION

#### THREE GENERATIONS OF TTL

Transistor-transistor logic has been the dominant technology for digital circuits since it was developed in the mid-1960's. It has proven itself to be manufacturable in high volume using an extremely reliable process technology. The processes used for TTL have evolved over the years, making components smaller, faster and less expensive. Relative to a TTL gate manufactured in 1966, a gate on a circuit manufactured today occupies 1/5 the area, consumes 1/10 the power, is twice as fast and costs less than 1/100 the price.

The circuits built using TTL technology have gone through two generations; the Am2900 Family represents the beginning of the third. Each generation consists of circuits which are fundamental building blocks of systems — circuits which can be interconnected in many different ways to build many different systems. Only by producing such universal circuits can manufacturing volumes be high enough to generate the rapid cost reductions characteristic of the integrated circuit industry.

The quality which distinguishes one generation from another is the level of integration used, and, because of the level of integration, the philosophy behind the circuit.

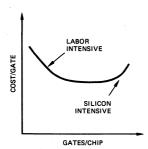

If one draws a curve plotting the cost of an individual gate against the number of gates on a chip, Figure 1 results.

Figure 1.

At the left, cost per gate is inversely proportional to the number of gates on the chip. The chip is small enough that it does not represent a significant portion of the cost of the product — it is virtually free. The cost of the product is composed of labor in assembly and test, the cost of processing an order, shipping and fixed overhead. Doubling the number of gates on the chip doesn't materially affect the cost so the cost per gate halves. As the number of gates per chip increases, the die begins to cost more, reversing the downward trend. As die cost dominates, the cost per gate remains relatively flat until the yield of the die begins to decline markedly. The cost per gate then begins to rise again. The lowest cost per gate is achieved at a level of integration corresponding to the flat region. This is the optimum level of integration.

As technology improves, costs are constantly reduced and the optimum level of integration occurs at more and more gates per chip.

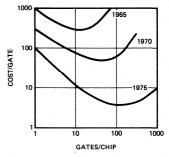

The three curves of Figure 2 are the reason for the three generations of TTL. Each generation has consisted of fundamental system building blocks designed to take advantage of the optimum level of integration at the time.

Figure 2.

#### **GENERATION I - SSI, 1965**

In 1965, the optimum level of integration was three-to-six gates per chip. Users were delighted to buy such chips at \$10-20 each. The circuits were useful in many systems. They consisted of gates — the 7400, 7410, 7420 — and, pressing the state of the art, some flip-flops. They were fundamental building blocks.

#### **GENERATION II - MSI, 1970**

Beginning around 1968, it became economical to put more gates on a chip and the industry was faced with a problem: How does one put 20 gates on a chip and build a universal building block? Clearly, one answer was to bring the inputs and outputs off chip as had been done before. But that was the wrong answer. The right answer was to redefine fundamental building blocks. The new building blocks fell into seven categories:

- Counters

- Decoders

- Multiplexers

- Operators (adders, comparators)

- Encoders

- Registers

- Latches

All systems could be defined in terms of these seven functions, and integrated circuits could be defined at the 20-50 gate/chip level which performed these functions efficiently. This, of course, is MSI. Over the last six or seven years, more and more circuits of this type have been introduced, utilizing standard gold-doped technology, low-power TTL, high-speed TTL, Schottky TTL, and now low-power Schottky TTL technology. Today, there are over 250 different MSI circuits and new ones appear every month. But in today's technology, many of these circuits are not particularly cost effective. They are too small for today's technology and their costs are labor intensive. (Labor costs do not follow traditional semiconductor pricing patterns.) In 1976, the optimum level of integration for bipolar logic is around 300 gates/chip.

#### GENERATION III - The Am2900 Family, 1976

At a 300-gate-per-chip level of integration, one does not build counters, decoders, and multiplexers. A new definition of fundamental system functions is needed. Advanced Micro Devices has defined these eight categories:

- Data Manipulation

- Microprogram Control

- Macroprogram Control

- Priority Interrupt

- Direct Memory Access

- I/O Control

- Memory Control

- Front Panel Control

The Am2900 Family consists of circuits designed to perform those functions efficiently. They are fundamental system building blocks; they contain hundreds of gates per chip; they are fast — utilizing Low-Power Schottky TTL technology; they are expandable; they are flexible — useful in emulation; and they are driven under microprogram control.

Hello, LSI. Introducing the Am2900 Family.

#### THE Am2900 FAMILY

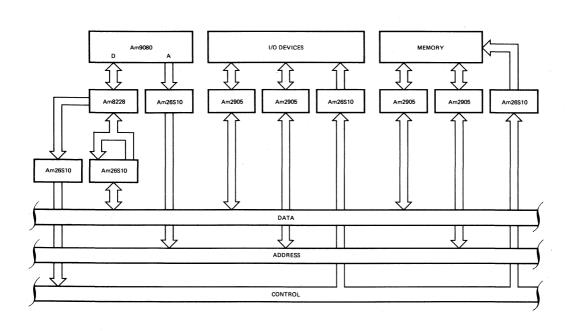

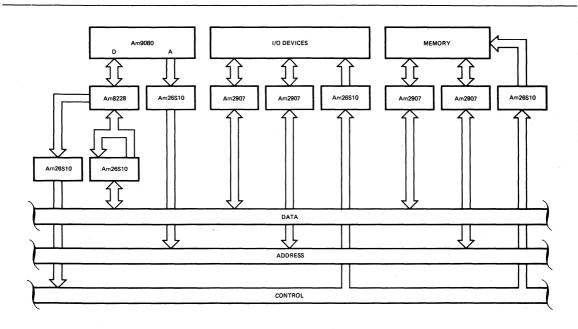

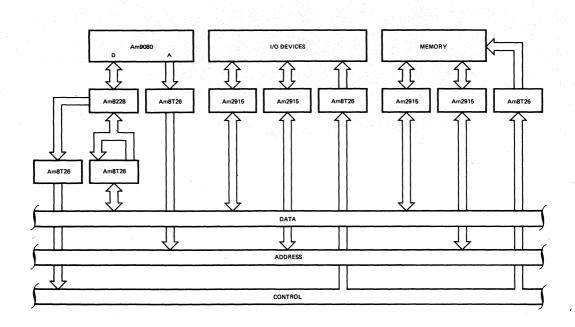

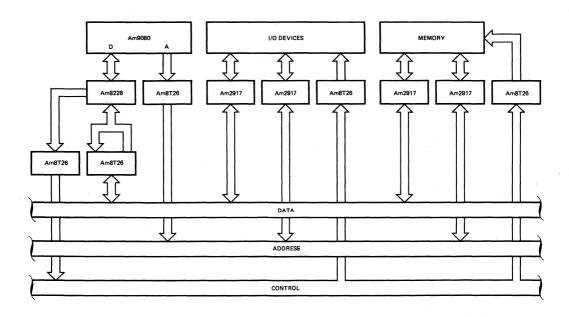

The Am2900 Family consists of a series of LSI building blocks designed for use in microprogrammed computers and controllers. Each device is designed to be expandable and sufficiently flexible to be suitable for emulation of many existing machines. It is the wide variety of machine architectures possible with the Am2900 Family which sets it apart from the fixed-instruction microprocessors such as the Am9080A.

While an Am9080A can be used to build a microcomputer with only four or five packages, an Am2900 design will require 30 or 40 or more. The Am9080A design will, therefore, almost always be cheaper. But the Am9080A, or any other fixed-instruction processor, can execute only one instruction set, so it is not really suitable for emulation of another machine.

Moreover, a fixed-instruction processor operates only on words of a single length, usually eight bits. An Am2900 design, on the other hand, can be constructed for any word length which is a multiple of four bits.

Many applications require specialized operations to be performed at relatively high speed. Such functions as multiply and divide and special graphic control operations, can be done in microcode 10-100 times faster than in fixed-instruction MOS processors.

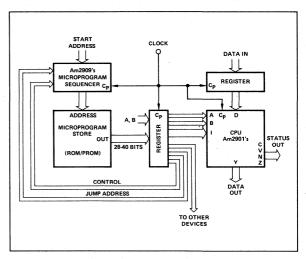

#### MICROPROGRAMMED ARCHITECTURE

Most small processors today are being designed using a technique called microprogramming. In microprogrammed systems, a large portion of the system's control is performed by a read only memory (usually PROM) rather than large arrays of gates and flip-flops. This technique frequently reduces the package count in the controller and provides a highly ordered structure in the controller, not present when random logic is used. Moreover, microprogramming makes changes in the machines' instruction set very simple to perform — reducing the post-production engineering costs for the system substantially.

The Am2900 Family of Bipolar LSI devices has been designed for use in microprogrammed systems. Each device performs a basic system function and is driven by a set of control lines from a microinstruction.

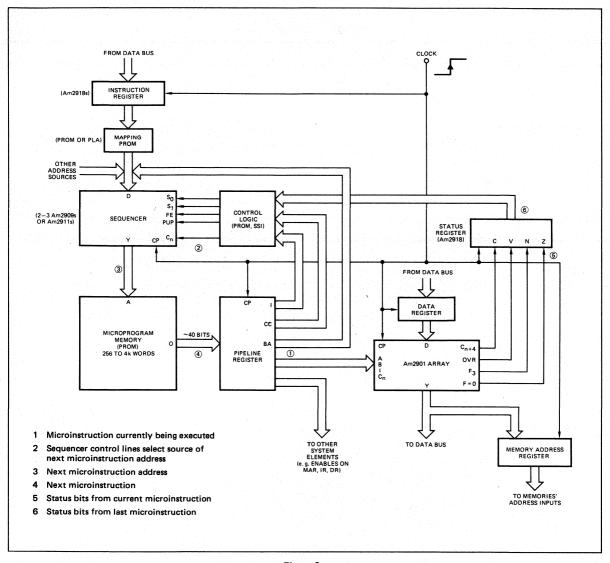

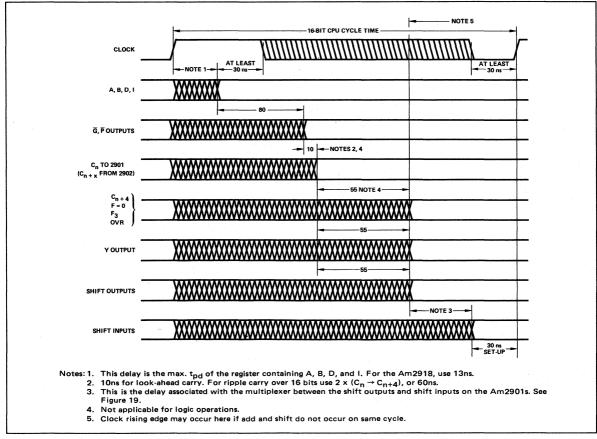

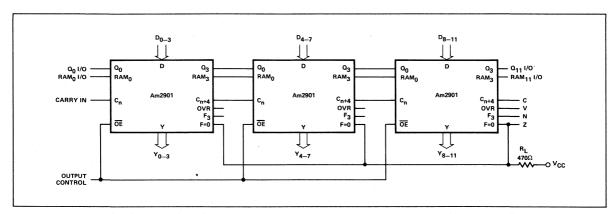

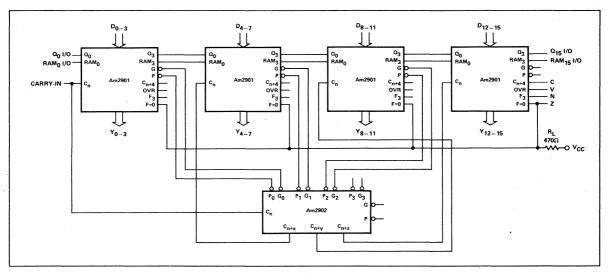

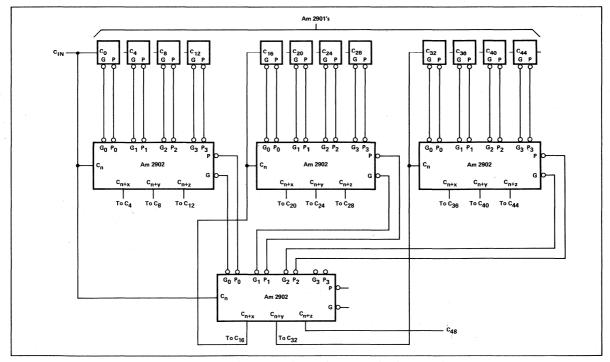

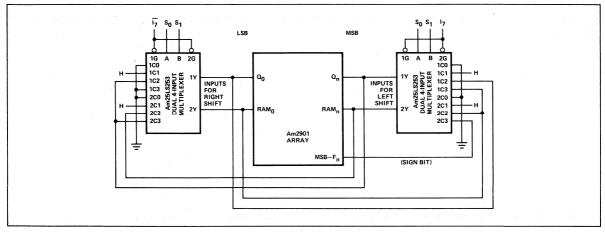

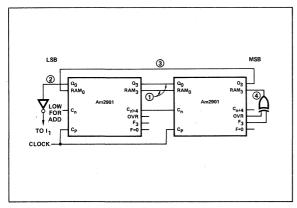

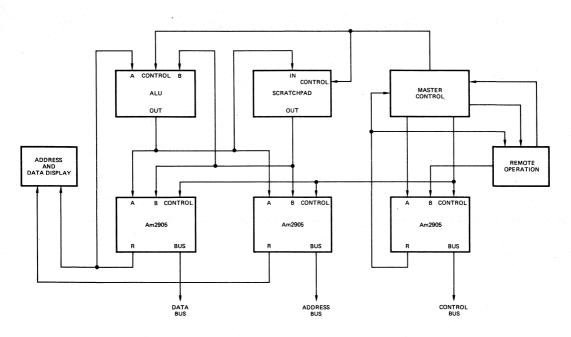

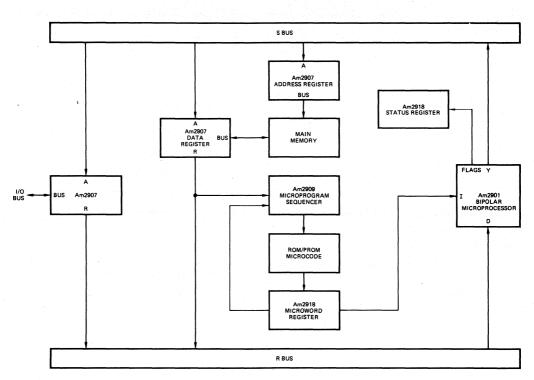

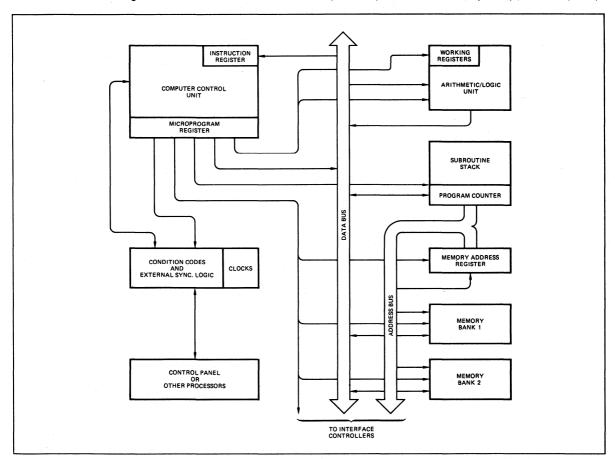

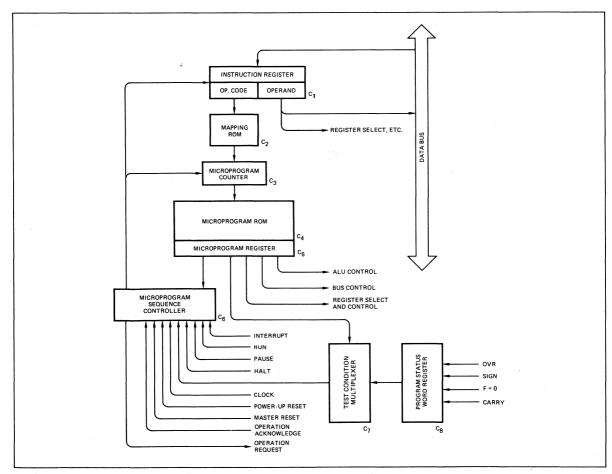

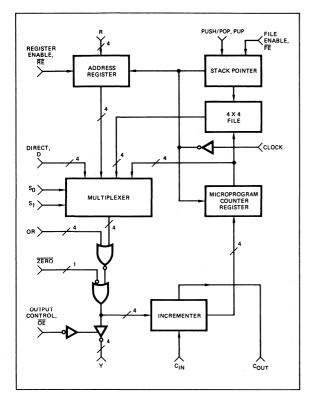

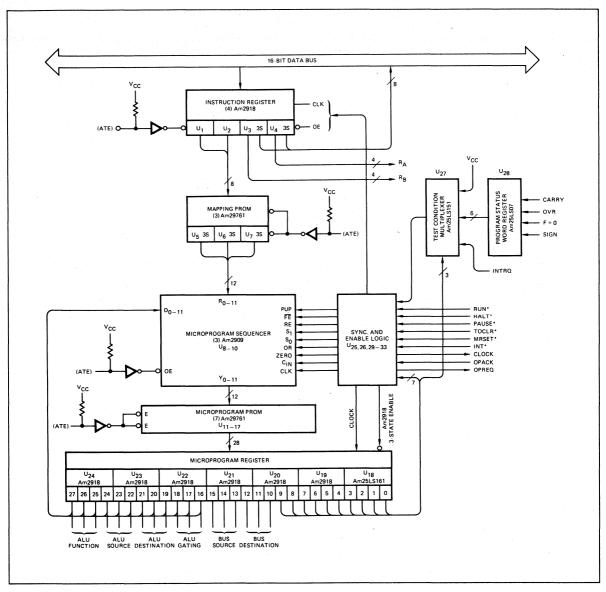

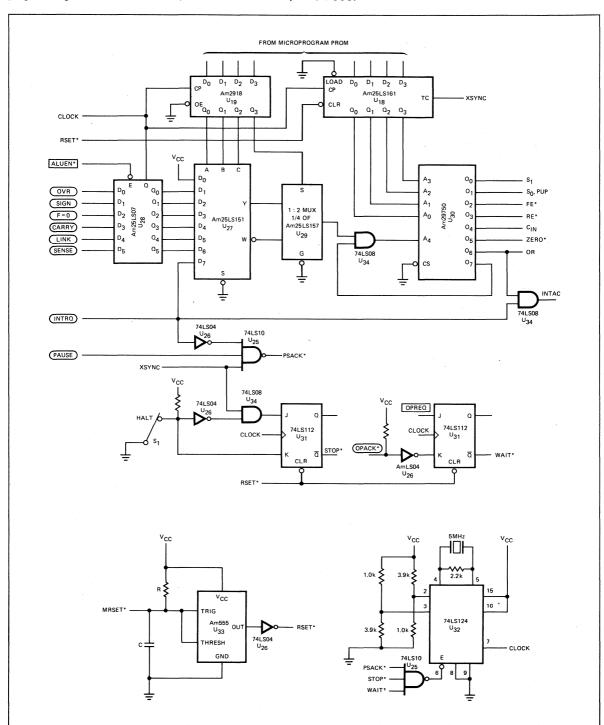

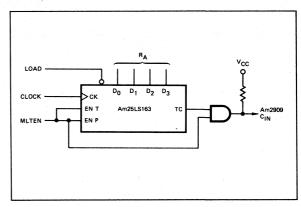

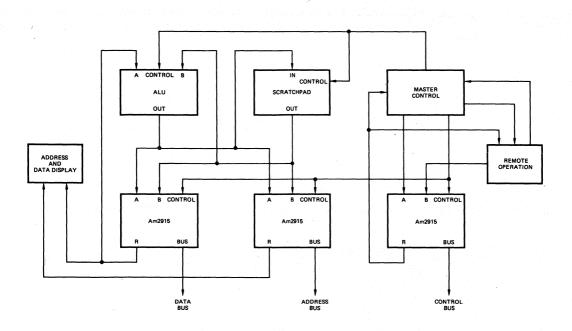

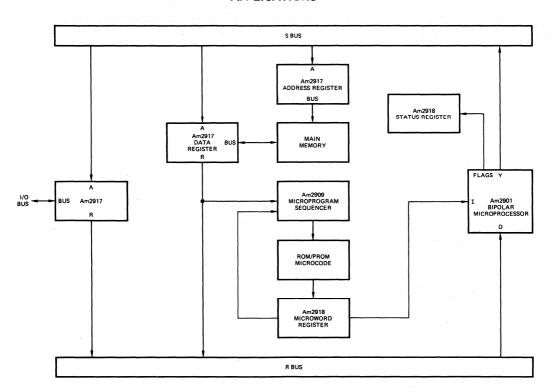

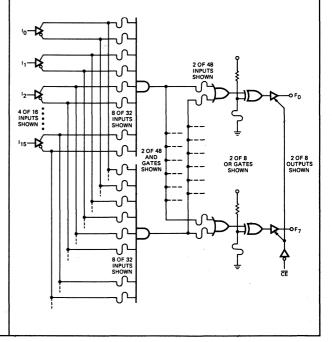

Figure 3 illustrates a typical system architecture. There are two "sides" to the system. At the left is the control circuitry and on the right is the data manipulation circuitry. The block labeled "2901 array" consists of the ALU, scratchpad registers, data steering logic (all internal to the Am2901's), plus left/

right shift control and carry lookahead circuit. Data is processed by moving it from main memory (not shown) into the 2901 registers, performing the required operations on it and returning the result to main memory. Memory addresses may also be generated in the 2901's and sent out to the memory address register (MAR). The four status bits from the 2901's ALU are captured in the status register after each operation.

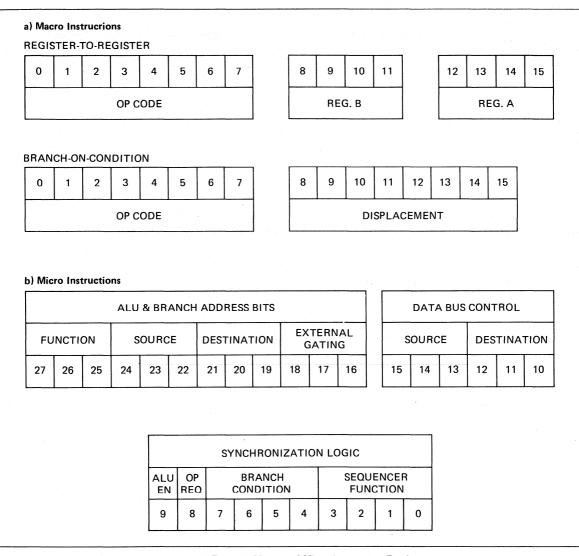

The logic on the left side is the control section of the computer. This is where the Am2909 or Am2911 is used. The entire system is controlled by a memory, usually PROM, which contains long words called microinstructions. Each microinstruction contains bits to control each of the data manipulation elements in the system. There are, for example, nine bits for the 2901 instruction lines, eight bits for the A and B register addresses, two or three bits to control the shifting multiplexers at the ends of the 2901 array (Figure 19 or 2901 data sheet), and bits to control the register enables on the MAR, instruction register, and various bus transceivers. When the bits in a microinstruction are applied to all the data elements and everything is clocked, then one small operation (such as a data transfer or a register-to-register add) will occur.

A "machine instruction" (such as a minicomputer instruction or a 9080A instruction) is performed by executing several microinstructions in sequence. Each microinstruction therefore contains not only bits to control the data hardware, but also bits to define the location in PROM of the next microinstruction to be executed. The fields are labeled in Figure 3 as I, CC, and BA. The I field controls the sequencer. It indicates where the next address is located — the  $\mu$ PC, the stack, or the direct inputs — and whether the stack is to be pushed or popped.

The CC field contains bits indicating the conditions under which the I field applies. These are compared with the condition codes in the status register and may cause modification to the I field. The comparing and modification occurs in the block labeled "control logic". Frequently this is just a PROM. The BA field is a branch address or the address of a subroutine.

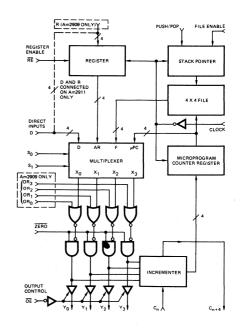

#### **PIPELINING**

The address for the microinstructions is generated by the sequencer, starting from a clock edge. The address goes from the sequencer to the ROM and, an access time later, the microinstruction is at the ROM outputs.

A pipeline register is a register placed on the output of the microprogram memory to essentially split the system in two. The pipeline register contains the microinstruction currently being executed ①. (Refer to the circled numbers in Figure 3.) The data manipulation control bits go out to the system elements and a portion of the microinstruction is returned to the sequencer 2 to determine the address of the next microinstruction to be executed. That address (3) is sent to the ROM and the next microinstruction (4) sits at the input of the pipeline register. So while the 2901's are executing one instruction, the next instruction is being fetched from ROM. Note that there is no sequencial logic in the sequencer between the select lines and the output. This is important because the loop 1) to 2) to 3) to 4) must occur during a single clock cycle. During the same time, the loop from 1 to 5 must occur in the 2901's. These two paths are roughly the same (around 200ns worst case for a 16-bit system). The presence of the pipeline register allows the microinstruction fetch to occur in parallel with the data operation rather than serially, allowing the clock frequency to be doubled.

Figure 3.

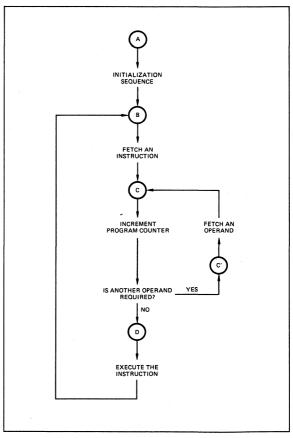

The system shown in Figure 3 works as follows. A sequence of microinstructions in the PROM is executed to fetch an instruction from main memory. This requires that the program counter, often in a 2901 working register, be sent to the memory address register and incremented. The data returned from memory is loaded into the instruction register. The contents of the instruction register is passed through a PROM or PLA to generate the address of the first microinstruction which must be executed to perform the required function. A branch to this address occurs through the sequencer. Several microinstructions may be executed to fetch data from memory, perform ALU operations, test for overflow, and so forth. Then a branch will be made back to the instruction fetch cycle. At this point, there may be branches to other sections of micro-

code. For example, the machine might test for an interrupt here and obtain an interrupt service routine address from another mapping ROM rather than start on the next machine instruction. There are obviously many possibilities. Throughout this data book, in application notes, and within data sheets, some suggested techniques will be found.

Additional application notes are in preparation and are planned for publication during 1976. Advanced Micro Devices' Applications' staff is available to answer questions and provide technical assistance as well. They may be reached by calling (408) 732-2400, or, outside California (800) 538-7904. Ask for Am2900 Family Applications.

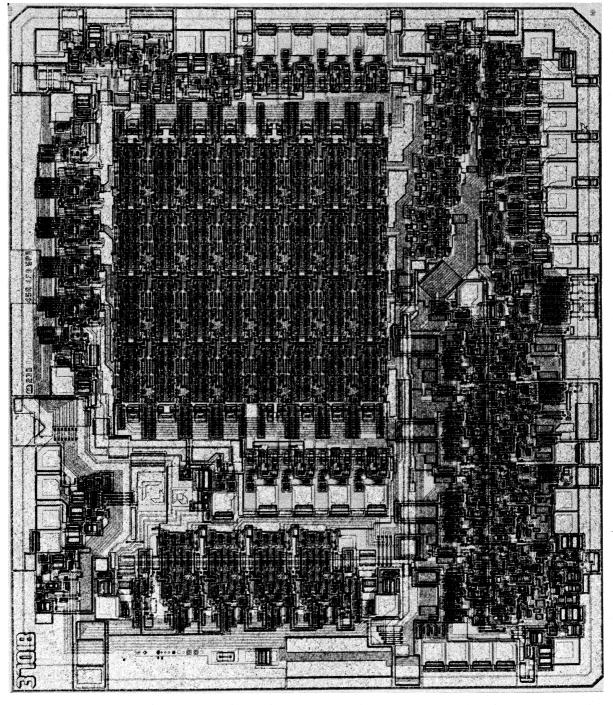

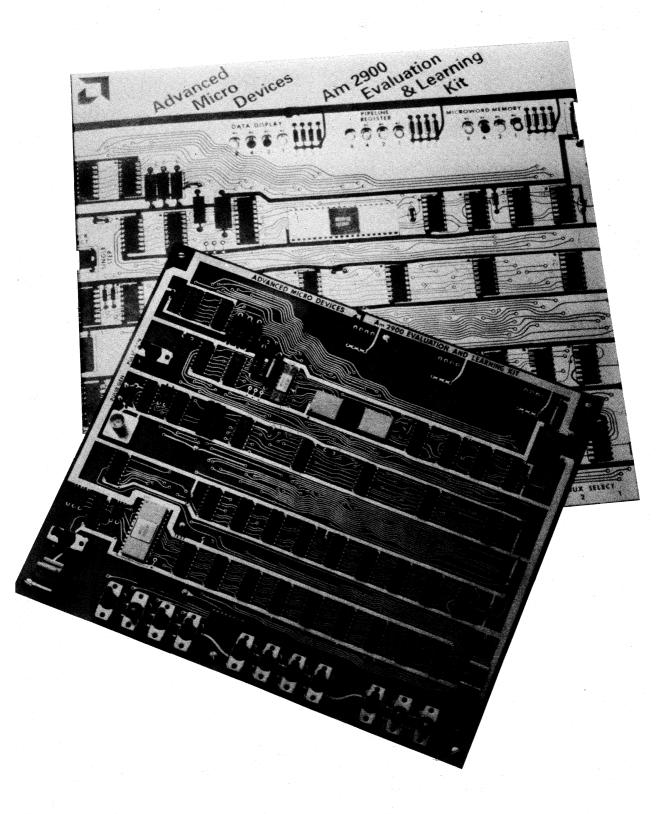

## Am2901 Photomicrograph

## Am2901

#### Four-Bit Bipolar Microprocessor Slice

#### **DISTINCTIVE CHARACTERISTICS**

- Two-address architecture —

Independent simultaneous access to two working registers saves machine cycles.

- Eight-function ALU —

Performs addition, two subtraction operations, and five logic functions on two source operands.

• Flexible data source selection -

ALU data is selected from five source ports for a total of 203 source operand pairs for every ALU function.

Left/right shift independent of ALU —

Add and shift operations take only one cycle.

• Four status flags -

Carry, overflow, zero, and negative.

Expandable —

Connect any number of Am2901's together for longer word lengths.

Microprogrammable —

Three groups of three bits each for source operand, ALU function, and destination control.

#### **GENERAL DESCRIPTION**

The four-bit bipolar microprocessor slice is designed as a high-speed cascadable element intended for use in CPU's, peripheral controllers, programmable microprocessors and numerous other applications. The microinstruction flexibility of the Am2901 will allow efficient emulation of almost any digital computing machine.

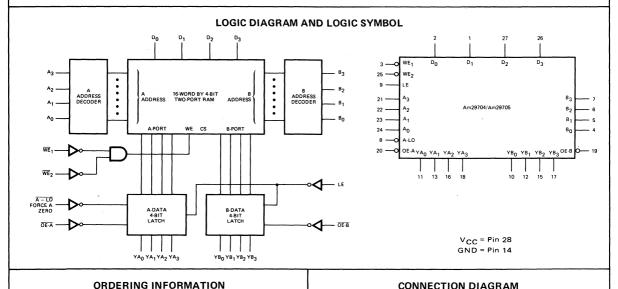

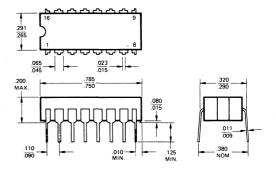

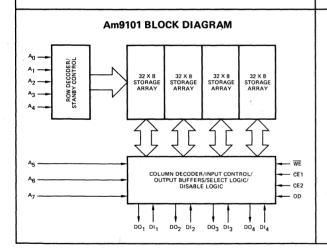

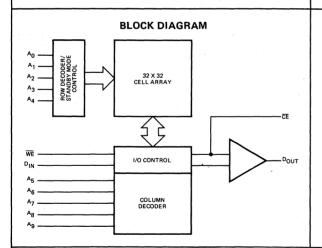

The device, as shown in the block diagram below, consists of a 16-word by 4-bit two-port RAM, a high-speed ALU, and the associated shifting, decoding and multiplexing circuitry. The nine-bit microinstruction word is organized into three groups of three bits each and selects the ALU source operands, the ALU function, and the ALU destination register. The microprocessor is cascadable with full look-ahead or with ripple carry, has three-state outputs, and provides various status flag outputs from the ALU. Advanced low-power Schottky processing is used to fabricate this 40-lead LSI chip.

#### **TABLE OF CONTENTS**

| Block Diagram         | . 3 |

|-----------------------|-----|

| Function Tables       | 4   |

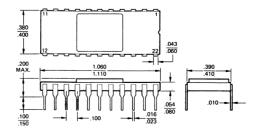

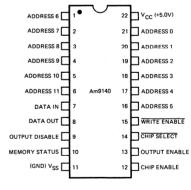

| Package Outlines      | 6   |

| Connection Diagram    | 7   |

| Pin Definitions       | 7   |

| Screening             | 8   |

| Order Codes           | 8   |

| DC Characteristics    | 9   |

| AC Characteristics    | 10  |

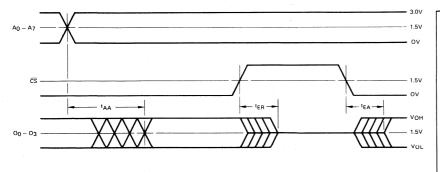

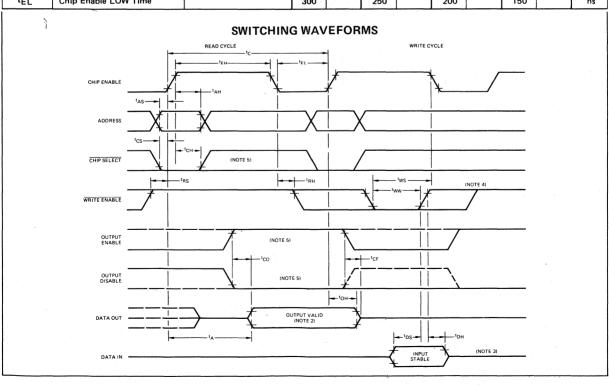

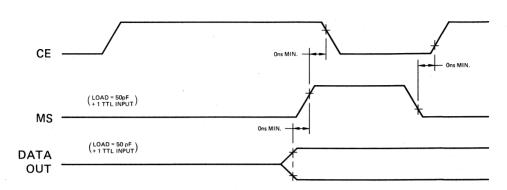

| Switching Waveforms   | 11  |

| Applications          | 13  |

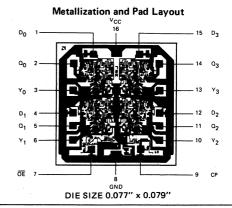

| Metallization Pattern | 7   |

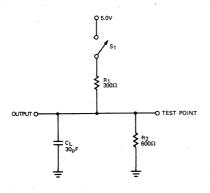

| Burn-in Circuit       | 12  |

| Microphotograph       | 18  |

|                       |     |

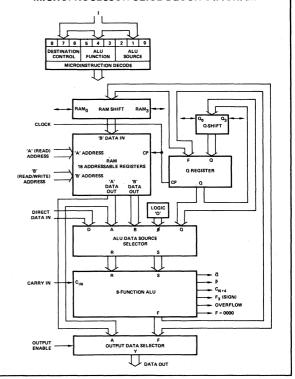

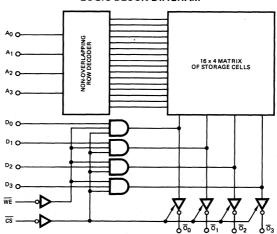

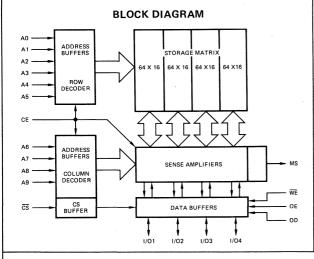

#### MICROPROCESSOR SLICE BLOCK DIAGRAM

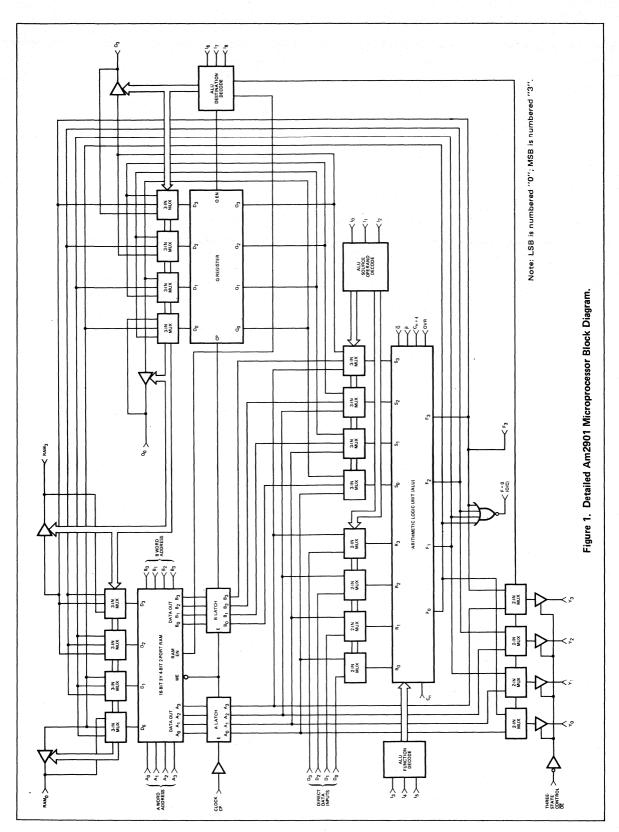

#### **ARCHITECTURE**

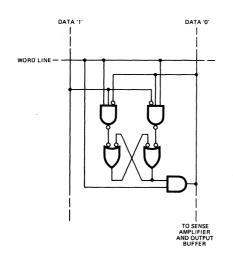

A detailed block diagram of the bipolar microprogrammable microprocessor structure is shown in Figure 1. The circuit is a four-bit slice cascadable to any number of bits. Therefore, all data paths within the circuit are four bits wide. The two key elements in the Figure 1 block diagram are the 16-word by 4-bit 2-port RAM and the high-speed ALU.

Data in any of the 16 words of the Random Access Memory (RAM) can be read from the A-port of the RAM as controlled by the 4-bit A address field input. Likewise, data in any of the 16 words of the RAM as defined by the B address field input can be simultaneously read from the B-port of the RAM. The same code can be applied to the A select field and B select field in which case the identical file data will appear at both the RAM A-port and B-port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the file (word) defined by the B address field of the RAM. The RAM data input field is driven by a 3-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This three-input multiplexer scheme allows the data to be shifted up one bit position, shifted down one bit position, or not shifted in either direction.

The RAM A-port data outputs and RAM B-port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is LOW. This eliminates any possible race conditions that could occur while new data is being written into the RAM.

The high-speed Arithmetic Logic Unit (ALU) can perform three binary arithmetic and five logic operations on the two 4-bit input words R and S. The R input field is driven from a 2-input multiplexer, while the S input field is driven from a 3-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a "zero" source operand.

Referring to Figure 1, the ALU R-input multiplexer has the RAM A-port and the direct data inputs (D) connected as inputs. Likewise, the ALU S-input multiplexer has the RAM A-port, the RAM B-port and the Q register connected as inputs.

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. These five inputs, when taken two at a time, result in ten possible combinations of source operand pairs. These combinations include AB, AD, AQ, AO, BD, BQ, BO, DQ, DO and QO. It is apparent that AD, AQ and AO are somewhat redundant with BD, BQ and BO in that if the A address and B address are the same, the identical function results. Thus, there are only seven completely non-redundant source operand pairs for the ALU. The Am2901 microprocessor implements eight of these pairs. The microinstruction inputs used to select the ALU source operands are the I0, I1, and I2 inputs. The definition of I0, I1, and I2 for the eight source operand combinations are as shown in Figure 2. Also shown is the octal code for each selection.

The two source operands not fully described as yet are the D input and Q input. The D input is the four-bit wide direct data field input. This port is used to insert all data into the working registers inside the device. Likewise, this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines but it can also be used as an accumulator or holding register for some applications.

The ALU itself is a high-speed arithmetic/logic operator capable of performing three binary arithmetic and five logic functions. The  $I_3$ ,  $I_4$ , and  $I_5$  microinstruction inputs are used to select the

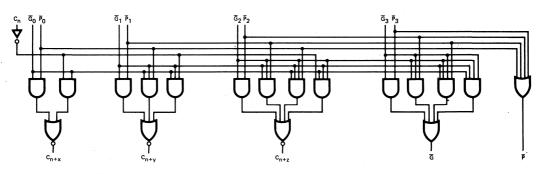

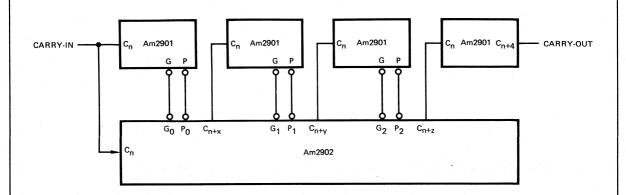

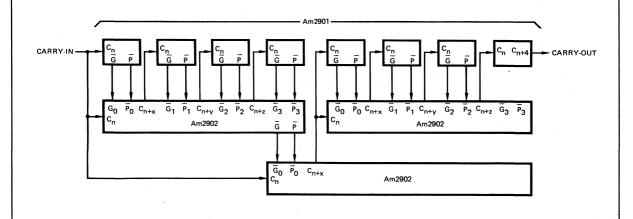

ALU function. The definition of these inputs is shown in Figure 3. The octal code is also shown for reference. The normal technique for cascading the ALU of several devices is in a look-ahead carry mode. Carry generate,  $\overline{\bf G}$ , and carry propagate,  $\overline{\bf P}$ , are outputs of the device for use with a carry-look-ahead-generator such as the Am2902 ('182). A carry-out,  $C_{n+4}$ , is also generated and is available as an output for use as the carry flag in a status register. Both carry-in ( $C_n$ ) and carry-out ( $C_{n+4}$ ) are active HIGH.

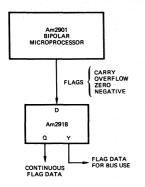

The ALU has three other status-oriented outputs. These are  $F_3$ , F=0, and overflow (OVR). The  $F_3$  output is the most significant (sign) bit of the ALU and can be used to determine positive or negative results without enabling the three-state data outputs.  $F_3$  is non-inverted with respect to the sign bit output  $Y_3$ . The F=0 output is used for zero detect. It is an open-collector output and can be wire OR'ed between microprocessor slices. F=0 is HIGH when all F outputs are LOW. The overflow output (OVR) is used to flag arithmetic operations that exceed the available two's complement number range. The overflow output (OVR) is HIGH when overflow exists. That is, when  $C_{n+3}$  and  $C_{n+4}$  are not the same polarity.

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register. Eight possible combinations of ALU destination functions are available as defined by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. These combinations are shown in Figure 4.

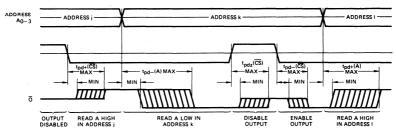

The four-bit data output field (Y) features three-state outputs and can be directly bus organized. An output control  $(\overline{OE})$  is used to enable the three-state outputs. When  $\overline{OE}$  is HIGH, the Y outputs are in the high-impedance state.

A two-input multiplexer is also used at the data output such that either the A-port of the RAM or the ALU outputs (F) are selected at the device Y outputs. This selection is controlled by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. Refer to Figure 4 for the selected output for each microinstruction code combination.

As was discussed previously, the RAM inputs are driven from a three-input multiplexer. This allows the ALU outputs to be entered non-shifted, shifted up one position (X2) or shifted down one position ( $\dot{\tau}2$ ). The shifter has two ports; one is labeled RAM0 and the other is labeled RAM3. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer. Thus, in the shift up mode, the RAM3 buffer is enabled and the RAM0 multiplexer input is enabled. Likewise, in the shift down mode, the RAM0 buffer and RAM3 input are enabled. In the no-shift mode, both buffers are in the high-impedance state and the multiplexer inputs are not selected. This shifter is controlled from the  $I_6$ ,  $I_7$  and  $I_8$  microinstruction inputs as defined in Figure 4.

Similarly, the Q register is driven from a 3-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-down mode, the multiplexer selects the Q register data appropriately shifted up or down. The Q shifter also has two ports; one is labeled  $\mathsf{Q}_0$  and the other is  $\mathsf{Q}_3$ . The operation of these two ports is similar to the RAM shifter and is also controlled from  $\mathsf{I}_6$ ,  $\mathsf{I}_7$ , and  $\mathsf{I}_8$  as shown in Figure 4.

The clock input to the Am2901 controls the RAM, the Q register, and the A and B data latches. When enabled, data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is LOW, the latches are closed and will retain the last data entered. If the RAM-EN is enabled, new data will be written into the RAM file (word) defined by the B address field when the clock input is LOW.

|     | MICRO CODE |     |               |   | OURCE<br>ANDS |

|-----|------------|-----|---------------|---|---------------|

| 12  | 11         | 10  | Octal<br>Code | R | s             |

| L   | L          | L   | 0             | A | 0             |

| L   | L          | H   | 1             | Α | В             |

| L   | н          | L   | 2             | 0 | Q             |

| L   | н          | н   | 3             | 0 | В             |

| н   | L          | . L | 4             | 0 | Α             |

| н   | L          | н   | 5             | D | Α             |

| , H | H          | L   | 6             | D | Q             |

| H   | H          | . н | 7             | D | 0             |

| Figure | 2 | Source | Operand | Control |

|--------|---|--------|---------|---------|

| MICRO CODE |    |                | ALU           |            |        |  |

|------------|----|----------------|---------------|------------|--------|--|

| 15         | 14 | l <sub>3</sub> | Octal<br>Code | Function   | Symbol |  |

| L          | L  | L              | 0             | R Plus S   | R+S    |  |

| L          | E  | H              | -1            | S Minus R  | S - R  |  |

| L          | н  | · L            | 2             | R Minus S  | R – S  |  |

| L          | н  | н              | 3             | RORS       | RVS    |  |

| H          | L  | L              | 4             | RANDS      | RAS    |  |

| н          | L  | н              | 5             | RANDS      | Ř∧s    |  |

| н          | н  | L              | 6             | R EX-OR S  | R ¥ S  |  |

| н          | н  | н              | 7             | R EX-NOR S | R ¥ S  |  |

Figure 3. ALU Function Control.

|    | MICRO CODE |    | CRO CODE RAM Q-REG. FUNCTION FUNCTION |       |         |       | Y       | RA<br>Y SHIF |                  | SHIF             | -               |                 |

|----|------------|----|---------------------------------------|-------|---------|-------|---------|--------------|------------------|------------------|-----------------|-----------------|

| 18 | 17         | 16 | Octal<br>Code                         | Shift | Load    | Shift | Load    | OUTPUT       | RAM <sub>0</sub> | RAM <sub>3</sub> | Q <sub>0</sub>  | α3              |

| L  | L          | L  | 0                                     | ×     | NONE    | NONE  | F→Q     | F            | ×                | ×                | ×               | ×               |

| L  | L          | н  | 1                                     | ×     | NONE    | ×     | NONE    | F            | ×                | ×                | ×               | ×               |

| L  | н          | L  | 2                                     | NONE  | F→B     | ×     | NONE    | А            | ×                | ×                | X               | ×               |

| L. | н          | н  | 3                                     | NONE  | F→B     | ×     | NONE    | F            | ×                | х                | ×               | ×               |

| н  | L          | L  | 4                                     | DOWN  | F/2 → B | DOWN  | Q/2 → Q | F            | F <sub>0</sub>   | IN <sub>3</sub>  | σo              | IN <sub>3</sub> |

| н  | L          | н  | 5                                     | DOWN  | F/2 → B | ×     | NONE    | F            | F <sub>0</sub>   | IN <sub>3</sub>  | <b>a</b> 0      | ×               |

| н  | н          | L  | 6                                     | UP    | 2F → B  | UP    | 2Q → Q  | F            | IN <sub>0</sub>  | F <sub>3</sub>   | IN <sub>O</sub> | 03              |

| н  | н          | н  | 7                                     | UP    | 2F → B  | х     | NONE    | F            | IN <sub>O</sub>  | F <sub>3</sub>   | x               | O3              |

X=Don't care. Electrically, the shift pin is a TTL input internally connected to a three-state output which is in the highimpedance state.

B = Register Addressed by B inputs.

Up is toward MSB, Down is toward LSB.

Figure 4. ALU Destination Control.

| <u> </u>         |                                                       |              |              |            | <del></del> | · · · · · · · · · · · · · · · · · · · |              |              |            |

|------------------|-------------------------------------------------------|--------------|--------------|------------|-------------|---------------------------------------|--------------|--------------|------------|

| \ <u>\</u>       | 210 OCTAL                                             | 0            | 1            | 2          | 3           | 4                                     | 5            | 6            | 7          |

| OLS<br>TA4<br>L3 | ALU<br>Source<br>ALU<br>Function                      | A, Q         | А, В         | ο, α       | О, В        | О, А                                  | D, A         | D, Q         | D, O       |

| 0                | C <sub>n</sub> = L<br>R Plus S<br>C <sub>n</sub> = H  | A+Q<br>A+Q+1 | A+B<br>A+B+1 | Q<br>Q+1   | B<br>B+1    | A<br>A+1                              | D+A<br>D+A+1 | D+Q<br>D+Q+1 | D<br>D+1   |

| 1                | C <sub>n</sub> = L<br>S Minus R<br>C <sub>n</sub> = H | Q-A-1<br>Q-A | B-A-1        | Q-1<br>Q   | B-1<br>B    | A-1<br>A                              | A-D-1        | Q-D-1<br>Q-D | -D-1<br>-D |

| 2                | C <sub>n</sub> = L<br>R Minus S<br>C <sub>n</sub> = H | A-Q-1<br>A-Q | A-B-1<br>A-B | −Q−1<br>−Q | −B−1<br>−B  | -A-1<br>-A                            | D-A-1<br>D-A | D-Q-1<br>D-Q | D-1<br>D   |

| 3                | R OR S                                                | ΑVQ          | A∨B          | Q          | В           | Α                                     | D∨A          | D∨Q          | D          |

| 4                | R AND S                                               | ΑΛQ          | A∧B          | 0          | 0           | 0                                     | D∧A          | DΛQ          | 0          |

| 5                | R AND S                                               | Ā∧Q          | Ā∧B          | Q          | В           | A                                     | Ō∧A          | ā∧Q          | 0          |

| 6                | R EX-OR S                                             | Α∀Q          | A∀B          | Q          | В           | A                                     | D∀A          | D∀Q          | D          |

| 7                | R EX-NORS                                             | Ā∀Q          | Ā∀B          | ā          | B           | Ā                                     | D∀A          | D∀Q          | ō          |

<sup>+ =</sup> Plus; - = Minus; V = OR; ∧ = AND; ₩ = EX-OR

Figure 5. Source Operand and ALU Function Matrix.

#### **SOURCE OPERANDS AND ALU FUNCTIONS**

There are eight source operand pairs available to the ALU as selected by the  $I_0$ ,  $I_1$ , and  $I_2$  instruction inputs. The ALU can perform eight functions; five logic and three arithmetic. The  $I_3$ ,  $I_4$ , and  $I_5$  instruction inputs control this function selection. The carry input,  $C_n$ , also affects the ALU results when in the arithmetic mode. The  $C_n$  input has no effect in the logic mode. When  $I_0$  through  $I_5$  and  $C_n$  are viewed together, the matrix of

Figure 5 results. This matrix fully defines the ALU/source operand function for each state.

The ALU functions can also be examined on a "task" basis, i.e., add, subtract, AND, OR, etc. In the arithmetic mode, the carry will affect the function performed while in the logic mode, the carry will have no bearing on the ALU output. Figure 6 defines the various logic operations that the Am2901 can perform and Figure 7 shows the arithmetic functions of the device. Both carry-in LOW ( $C_n = 0$ ) and carry-in HIGH ( $C_n = 1$ ) are defined in these operations.

| Octal<br>I543, I210      | Group  | Function                                                 |

|--------------------------|--------|----------------------------------------------------------|

| 4 0<br>4 1<br>4 5<br>4 6 | AND    | A∧Q<br>A∧B<br>D∧A<br>D∧Q                                 |

| 3 0<br>3 1<br>3 5<br>3 6 | OR     | AVQ<br>AVB<br>DVA<br>DVQ                                 |

| 6 0<br>6 1<br>6 5<br>6 6 | EX-OR  | A <del>∨</del> Q<br>D <del>∨</del> Q<br>D <del>∨</del> Q |

| 7 0<br>7 1<br>7 5<br>7 6 | EX-NOR | Ā∀Q<br>Ā∀B<br>D∀A<br>D∀Q                                 |

| 7 2<br>7 3<br>7 4<br>7 7 | INVERT | Q B A D                                                  |

| 6 2<br>6 3<br>6 4<br>6 7 | PASS   | Q<br>B<br>A<br>D                                         |

| 3 2<br>3 3<br>3 4<br>3 7 | PASS   | Q<br>B<br>A<br>D                                         |

| 4 2<br>4 3<br>4 4<br>4 7 | "ZERO" | 0<br>0<br>0                                              |

| 5 0<br>5 1<br>5 5<br>5 6 | MASK   | Ā∧Q<br>Ā∧B<br>Ō∧A<br>Ō∧Q                                 |

Figure 6. ALU Logic Mode Functions. (Cn Irrelevant)

| Octal      | C <sub>n</sub> = 0 | (Low)    | C <sub>n</sub> = 1 | (High)   |

|------------|--------------------|----------|--------------------|----------|

| l543, l210 | Group              | Function | Group              | Function |

| 0 0        |                    | A+Q      |                    | A+Q+1    |

| 0 1        | ADD                | A+B      | ADD plus           | A+B+1    |

| 0 5        |                    | D+A      | one                | D+A+1    |

| 0 6        |                    | D+Q      |                    | D+Q+1    |

| 0 2        |                    | a        |                    | Q+1      |

| 0.3        | PASS               | В        | Increment          | B+1      |

| 0 4        |                    | Α        |                    | A+1      |

| 0 7        |                    | D        |                    | D+1      |

| 1 2        |                    | Q-1      |                    | Q        |

| 1 3        | Decrement          | B-1      | PASS               | В        |

| 1 4        | a te               | A-1      |                    | A        |

| 2 7        |                    | D-1      |                    | D        |

| 2 2        |                    | -Q−1     |                    | -a       |

| 2 3        | 1's Comp.          | -B-1     | 2's Comp.          | -В       |

| 2 4        |                    | -A-1     | (Negate)           | -A       |

| 1 7        |                    | _D_1     |                    | -D       |

| 1 0        |                    | Q-A-1    |                    | Q-A      |

| 1 1        | Subtract           | B-A-1    | Subtract           | B-A      |

| 1 5        | (1's Comp)         | A-D-1    | (2's Comp)         | A-D      |

| 1 6        |                    | Q-D-1    |                    | Q_D      |

| 2 0        |                    | A-Q-1    |                    | A-Q      |

| 2 1        |                    | A-B-1    |                    | A-B      |

| 2 5        |                    | D-A-1    |                    | D-A      |

| 2 6        |                    | D-Q-1    | L                  | D_Q      |

Figure 7. ALU Arithmetic Mode Functions.

#### LOGIC FUNCTIONS FOR G, P, Cn+4, AND OVR

The four signals G, P,  $C_{n+4}$ , and OVR are designed to indicate carry and overflow conditions when the Am2901 is in the add or subtract mode. The table below indicates the logic equations for these four signals for each of the eight ALU functions. The R and S inputs are the two inputs selected according to Figure 2.

#### Definitions (+ = OR)

$$\begin{array}{llll} P_0 = R_0 + S_0 & G_0 = R_0 S_0 \\ P_1 = R_1 + S_1 & G_1 = R_1 S_1 \\ P_2 = R_2 + S_2 & G_2 = R_2 S_2 \\ P_3 = R_3 + S_3 & G_3 = R_3 S_3 \\ \\ C_4 = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0 + P_3 P_2 P_1 P_0 C_n \end{array}$$

$C_3 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_n$

| 1543 | Function | Ē                                                                                                                       | Ğ                                                                                                                                                        | C <sub>n+4</sub>                                                                      | OVR                                                                                |  |  |  |  |

|------|----------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

| 0    | R + S    | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>                                                             | $\overline{G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0}$                                                                                                     | C <sub>4</sub>                                                                        | C <sub>3</sub> <del>∀</del> C <sub>4</sub>                                         |  |  |  |  |

| 1    | S – R    | Same as R + S equations, but substitute $\overline{R_i}$ for $R_i$ in definitions                                       |                                                                                                                                                          |                                                                                       |                                                                                    |  |  |  |  |

| 2    | R – S    | Same as R + S equations, but substitute $\overline{S_i}$ for $S_i$ in definitions                                       |                                                                                                                                                          |                                                                                       |                                                                                    |  |  |  |  |

| 3    | Ŕ∨S      | LOW                                                                                                                     | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>                                                                                              | $\overline{P_3P_2P_1P_0} + C_n$                                                       | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> + C <sub>n</sub>       |  |  |  |  |

| 4    | R∧S      | LOW                                                                                                                     | $\overline{G_3 + G_2 + G_1 + G_0}$                                                                                                                       | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub> + C <sub>n</sub>    | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub> + C <sub>n</sub> |  |  |  |  |

| 5    | R∧s      | LOW Same as R \(\Lambda\) S equations, but substitute $\overline{R_i}$ for $R_i$ in definitions                         |                                                                                                                                                          |                                                                                       |                                                                                    |  |  |  |  |

| 6    | R∀S      | Same as $\overline{R} \overrightarrow{\forall} \overline{S}$ , but substitute $\overline{R}_i$ for $R_i$ in definitions |                                                                                                                                                          |                                                                                       |                                                                                    |  |  |  |  |

| 7    | R∀S      | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub>                                                       | G <sub>3</sub> +P <sub>3</sub> G <sub>2</sub> +P <sub>3</sub> P <sub>2</sub> G <sub>1</sub> +P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> G <sub>0</sub> | $ \frac{\overline{G_3 + P_3G_2 + P_3P_2G_1}}{+ P_3P_2P_1P_0 (G_0 + \overline{C_n})} $ | See note                                                                           |  |  |  |  |

Note:  $[\overline{P}_2 + \overline{G}_2 \overline{P}_1 + \overline{G}_2 \overline{G}_1 \overline{P}_0 + \overline{G}_2 \overline{G}_1 \overline{G}_0 C_n] + [\overline{P}_3 + \overline{G}_3 \overline{P}_2 + \overline{G}_3 \overline{G}_2 \overline{P}_1 + \overline{G}_3 \overline{G}_2 \overline{G}_1 \overline{P}_0 + \overline{G}_3 \overline{G}_2 \overline{G}_1 \overline{G}_0 C_n]$

+ = OR

Figure 8.

Figure 9.

Figure 10.

#### PIN DEFINITIONS

- A<sub>0-3</sub> The four address inputs to the register stack used to select one register whose contents are displayed through the A-port.

- B<sub>0-3</sub> The four address inputs to the register stack used to select one register whose contents are displayed through the B-port and into which new data can be written when the clock goes LOW.

- I<sub>0-8</sub> The nine instruction control lines to the Am2901, used to determine what data sources will be applied to the ALU (I<sub>012</sub>), what function the ALU will perform (I<sub>345</sub>), and what data is to be deposited in the Q-register or the register stack (I<sub>678</sub>).

- Q<sub>3</sub> A shift line at the MSB of the Q register (Q<sub>3</sub>) and the register stack (RAM<sub>3</sub>). Electrically these lines are three-state outputs connected to TTL inputs internal to the Am2901. When the destination code on I<sub>6</sub>78 indicates an up shift (octal 6 or 7) the three-state outputs are enabled and the MSB of the Q register is available on the Q<sub>3</sub> pin and the MSB of the ALU output is available on the RAM<sub>3</sub> pin. Otherwise, the three-state outputs are OFF (high-impedance) and the pins are electrically LS-TTL inputs. When the destination code calls for a down shift, the pins are used as the data inputs to the MSB of the Q register (octal 4) and RAM (octal 4 or 5).

- Q<sub>0</sub> Shift lines like Q<sub>3</sub> and RAM<sub>3</sub>, but at the LSB of the Q-register and RAM. These pins are tied to the Q<sub>3</sub> and RAM<sub>3</sub> pins of the adjacent device to transfer data between devices for up and down shifts of the Q register and ALU data.

- D<sub>0-3</sub> Direct data inputs. A four-bit data field which may be selected as one of the ALU data sources for entering data into the Am2901. D<sub>0</sub> is the LSB.

- Y<sub>0-3</sub> The four data outputs of the Am2901. These are three-state output lines. When enabled, they display either the four outputs of the ALU or the data on the A-port of the register stack, as determined by the destination code I<sub>678</sub>.

- OE Output Enable. When OE is HIGH, the Y outputs are OFF; when OE is LOW, the Y outputs are active (HIGH or LOW).

- P, G The carry generate and propagate outputs of the Am2901's ALU. These signals are used with the Am2902 for carry-lookahead. See Figure 8 for the logic equations.

- OVR Overflow. This pin is logically the Exclusive-OR of the carry-in and carry-out of the MSB of the ALU. At the most significant end of the word, this pin indicates that the result of an arithmetic two's complement operation has overflowed into the sign-bit. See Figure 8 for logic equation.

- ${\bf F}={\bf 0}$  This is an open collector output which goes HIGH (OFF) if the data on the four ALU outputs  ${\bf F_{0-3}}$  are all LOW. In positive logic, it indicates the result of an ALU operation is zero.

- C<sub>n</sub> The carry-in to the Am2901's ALU.

- Cn+4 The carry-out of the Am2901's ALU. See Figure 8 for equations.

- CP The clock to the Am2901. The Q register and register stack outputs change on the clock LOW-to-HIGH transition. The clock LOW time is internally the write enable to the 16 x 4 RAM which comprises the "master" latches of the register stack. While the clock is LOW, the "slave" latches on the RAM outputs are closed, storing the data previously on the RAM outputs. This allows synchronous master-slave operation of the register stack.

MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature                                 | -65°C to +150°C                 |

|-----------------------------------------------------|---------------------------------|

| Temperature (Ambient) Under Bias                    | –55°C to +125°C                 |

| Supply Voltage to Ground Potential                  | <br>–0.5 V to +6.3 V            |

| DC Voltage Applied to Outputs for HIGH Output State | -0.5 V to +V <sub>CC</sub> max. |

| DC Input Voltage                                    | −0.5 V to +5.5 V                |

| DC Output Current, Into Outputs                     | 30 mA                           |

| DC Input Current                                    | −30 mA to +5.0 mA               |

#### **OPERATING RANGE**

| P/N           | Ambient Temperature | V <sub>CC</sub>  |

|---------------|---------------------|------------------|

| Am2901PC, DC  | 0°C to +70°C        | 4.75 V to 5.25 V |

| Am2901 DM, FM | -55°C to +125°C     | 4.50 V to 5.50 V |

#### STANDARD SCREENING

(Conforms to MIL-STD-883 for Class C Parts)

|                             | MIL-STD-883            |                                    | Le           | vel          |

|-----------------------------|------------------------|------------------------------------|--------------|--------------|

| Step                        | Method                 | Conditions                         | Am2901PC, DC | Am2901DM, FM |

| Pre-Seal Visual Inspection  | 2010                   | В                                  | 100%         | 100%         |

| Stabilization Bake          | 1008                   | C 24-hour<br>150°C                 | 100%         | 100%         |

| Temperature Cycle           | 1010                   | C -65°C to +150°C<br>10 cycles     | 100%         | 100%         |

| Centrifuge                  | 2001                   | B 10,000 G                         | 100% *       | 100%         |

| Fine Leak                   | 1014                   | A 5 x 10 -8 atm-cc/cm <sup>3</sup> | 100% *       | 100%         |

| Gross Leak                  | 1014                   | C2 Fluorocarbon                    | 100% *       | 100%         |

| Electrical Test             | 5004                   | See below for                      | 1000/        | 1000/        |

| Subgroups 1 and 7           | 5004                   | definitions of subgroups           | 100%         | 100%         |

| Insert Additional Screening | nere for Class B Parts |                                    | 1.1.1.1      |              |

| Group A Sample Tests        |                        |                                    |              |              |

| Subgroup 1                  |                        |                                    | LTPD = 5     | LTPD = 5     |

| Subgroup 2                  |                        |                                    | LTPD = 7     | LTPD = 7     |

| Subgroup 3                  | 5005                   | See below for                      | LTPD = 7     | LTPD = 7     |

| Subgroup 7                  | 5005                   | definitions of subgroups           | LTPD = 7     | LTPD = 7     |

| Subgroup 8                  | 1. 1                   |                                    | LTPD = 7     | LTPD = 7     |

| Subgroup 9                  |                        |                                    | LTPD = 7     | LTPD = 7     |

<sup>\*</sup>Not applicable for Am2901PC

#### ADDITIONAL SCREENING FOR CLASS B PARTS

| 04                                                                     | MIL-STD-883 | 0                         | Level                                |  |  |

|------------------------------------------------------------------------|-------------|---------------------------|--------------------------------------|--|--|

| Step                                                                   | Method      | Conditions                | Am2901DMB, FM                        |  |  |

| Burn-In                                                                | 1015        | D 125°C<br>160 hours min. | 100%                                 |  |  |

| Electrical Test Subgroup 1 Subgroup 2 Subgroup 3 Subgroup 7 Subgroup 9 | 5004        |                           | 100%<br>100%<br>100%<br>100%<br>100% |  |  |

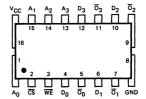

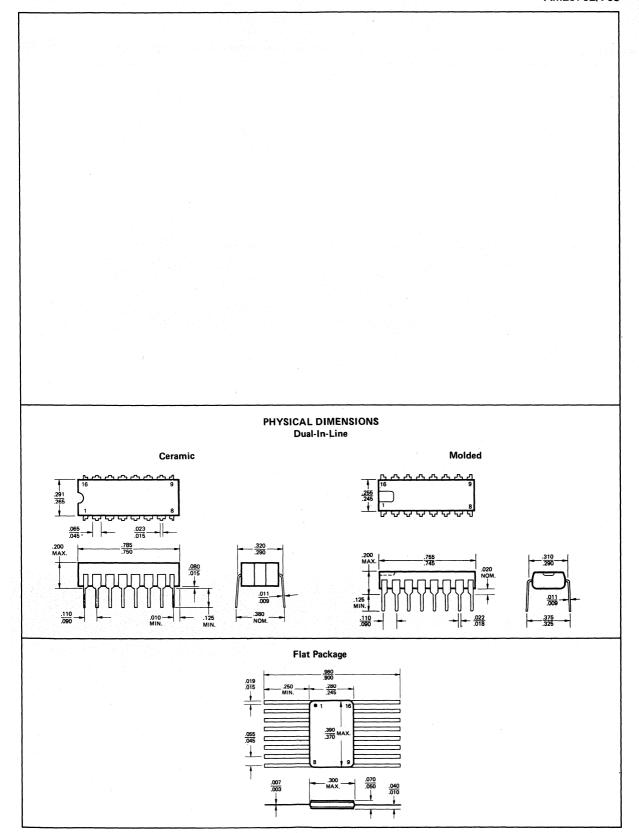

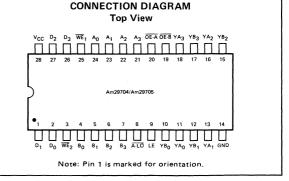

#### **ORDERING INFORMATION**

| Package            | Temperature     | Order    |

|--------------------|-----------------|----------|

| Type               | Range           | Number   |

| Molded DIP         | 0°C to +70°C    | AM2901PC |

| Hermetic DIP       | 0°C to +70°C    | AM2901DC |

| Hermetic DIP       | -55°C to +125°C | AM2901DM |

| Hermetic Flat Pack | -55°C to +125°C | AM2901FM |

| Dice               | 0°C to +70°C    | AM2901XC |

#### **GROUP A SUBGROUPS**

(as defined in MIL-STD-883, method 5005)

| Subgroup | Parameter | Temperature                           |

|----------|-----------|---------------------------------------|

| 1        | DC        | 25°C                                  |

| 2        | DC        | Maximum rated temperature             |

| 3        | DC        | Minimum rated temperature             |

| 7        | Function  | 25°C                                  |

| 8        | Function  | Maximum and minimum rated temperature |

| 9        | Switching | 25°C                                  |

| 10       | Switching | Maximum Rated Temeperature            |

| 11       | Switching | Minimum Rated Temperature             |

#### ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (Unless Otherwise Noted) (Group A, Subgroups 1, 2 and 3)

| rameters        | Description                               | Test Cond                                                                      | litions (Not                                                         | e 1)                                                 | Min. | Typ.<br>(Note 2) | Max.  | Units |

|-----------------|-------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------|------|------------------|-------|-------|

|                 |                                           |                                                                                | I <sub>OH</sub> = -1                                                 |                                                      | 2.4  |                  |       |       |

|                 |                                           |                                                                                | I <sub>OH</sub> = -1                                                 | .0mA, C <sub>n+4</sub>                               | 2.4  |                  |       |       |

|                 |                                           | Vcc = MIN.                                                                     |                                                                      | 300μA, OVR, P                                        | 2.4  |                  |       |       |

| VOH             | Output HIGH Voltage                       | V <sub>CC</sub> = MIN.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |                                                                      | 600μA, F <sub>3</sub>                                | 2.4  |                  |       | Volts |

|                 |                                           |                                                                                | I <sub>OH</sub> = -6                                                 | 600µA                                                | 2.4  |                  |       |       |

|                 |                                           |                                                                                | I <sub>OH</sub> = -1                                                 |                                                      | 2,4  |                  |       |       |

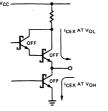

| ICEX            | Output Leakage Current                    | V <sub>CC</sub> = MIN., V <sub>OH</sub> =                                      |                                                                      |                                                      |      |                  | 250   | μА    |

|                 | for F = 0 Output                          | VIN = VIH or VIL                                                               | 1                                                                    |                                                      |      |                  |       |       |

|                 |                                           |                                                                                | I <sub>OL</sub> = 16                                                 | тд<br>Ү <sub>2</sub> , Ү <sub>3</sub> , <del>G</del> |      |                  | 0.5   |       |

| <b>v</b> oL     | Output LOW Voltage                        | V <sub>CC</sub> = MIN.,                                                        |                                                                      |                                                      |      |                  | 0.5   | Volts |

| VOL             | Output LOW Voltage                        | $V_{IN} = V_{IH}$ or $V_{IL}$                                                  |                                                                      |                                                      |      |                  | 0.5   | VOILS |

|                 |                                           |                                                                                |                                                                      |                                                      |      |                  | 0.5   |       |

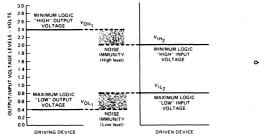

| V <sub>IH</sub> | Input HIGH Level                          | Guaranteed input log voltage for all inputs                                    | ical HIGH                                                            |                                                      | 2.0  |                  |       | Volts |

| VIL             | Input LOW Level                           | Guaranteed input log                                                           | nteed input logical LOW Military                                     |                                                      |      |                  | 0.7   | Volts |

| - 14            |                                           | voltage for all inputs                                                         |                                                                      | Commercial                                           |      |                  | 8.0   |       |

| V <sub>I</sub>  | Input Clamp Voltage                       | V <sub>CC</sub> = MIN., I <sub>IN</sub> = -                                    | -18mA                                                                |                                                      |      |                  | -1.5  | Volts |

|                 |                                           |                                                                                | Clock, O                                                             | Ē                                                    |      |                  | -0.36 |       |

|                 |                                           |                                                                                | A <sub>0</sub> , A <sub>1</sub> ,                                    | A <sub>2</sub> , A <sub>3</sub>                      |      |                  | -0.36 |       |

|                 |                                           |                                                                                | B <sub>0</sub> , B <sub>1</sub> , E                                  | B <sub>2</sub> , B <sub>3</sub>                      |      |                  | -0.36 | -     |

| I <sub>IL</sub> | Input LOW Current                         | V <sub>CC</sub> = MAX.                                                         | D <sub>0</sub> , D <sub>1</sub> ,                                    | D <sub>2</sub> , D <sub>3</sub>                      |      |                  | -0.72 | mA    |

| ·· <del>·</del> |                                           | V <sub>IN</sub> = 0.5V                                                         | 10, 11, 12                                                           |                                                      |      |                  | -0.36 |       |

|                 |                                           |                                                                                | 13, 14, 15                                                           |                                                      |      |                  | -0.72 |       |

|                 |                                           |                                                                                |                                                                      | 3, Q <sub>0, 3</sub> (Note 4)                        |      |                  | -0.8  |       |

|                 |                                           |                                                                                | Cn                                                                   |                                                      |      |                  | -3.6  |       |

|                 |                                           |                                                                                | Clock, O                                                             |                                                      |      |                  | 20    | *     |

|                 |                                           |                                                                                | A <sub>0</sub> , A <sub>1</sub> ,                                    |                                                      |      | -                | 20    |       |

|                 |                                           |                                                                                | B <sub>0</sub> , B <sub>1</sub> , I                                  |                                                      |      | ļ                | 20    |       |

| tтн             | Input HIGH Current                        | V <sub>CC</sub> = MAX.                                                         | D <sub>0</sub> , D <sub>1</sub> ,                                    |                                                      |      |                  | 40    | μΑ    |

|                 |                                           | V <sub>IN</sub> = 2.7V                                                         | 10, 11, 12                                                           |                                                      | 20   |                  |       |       |

|                 |                                           |                                                                                | 13, 14, 15                                                           | 3, Q <sub>0, 3</sub> (Note 4)                        |      |                  | 40    |       |

|                 |                                           |                                                                                | <u> </u>                                                             | 3, Q0, 3 (Note 4)                                    |      |                  | 100   |       |

|                 | Input HIGH Current                        | Voc = MAY Vivi =                                                               | C <sub>n</sub>                                                       |                                                      |      |                  | 1.0   | mA    |

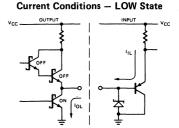

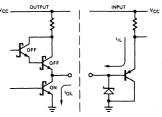

| 11              | input fridit current                      | V <sub>CC</sub> = MAX., V <sub>IN</sub> =                                      | T                                                                    | V <sub>O</sub> = 2.4V                                |      |                  | 50    | A     |

|                 |                                           |                                                                                | Y <sub>0</sub> , Y <sub>1</sub> ,<br>Y <sub>2</sub> , Y <sub>3</sub> | $V_0 = 0.5V$                                         |      |                  | -50   |       |

| lan.            |                                           |                                                                                | 2, 3                                                                 |                                                      |      | 1                | -50   | -     |

| lozh<br>lozh    | Off State (High Impedance) Output Current | V <sub>CC</sub> = MAX.                                                         | RAMO,                                                                | V <sub>O</sub> = 2.4V<br>(Note 4)                    |      |                  | 100   | μА    |

|                 |                                           |                                                                                | Q <sub>0,3</sub>                                                     | V <sub>O</sub> = 0.5V<br>(Note 4)                    |      |                  | -800  |       |

|                 |                                           | <u> </u>                                                                       | Y <sub>0</sub> , Y <sub>1</sub> ,                                    | Y <sub>2</sub> , Y <sub>3</sub> , $\overline{G}$     | -15  |                  | -40   |       |

|                 |                                           | V E 75V                                                                        | Cn+4                                                                 |                                                      | -15  |                  | -40   |       |

| Ios             | Output Short Circuit Current<br>(Note 3)  | V <sub>CC</sub> = 5.75V<br>V <sub>O</sub> = 0.5V                               | OVR, P                                                               |                                                      | -15  |                  | -40   | mA    |

|                 | (14016.9)                                 | * U = 0.3 v                                                                    | F <sub>3</sub>                                                       |                                                      | -15  |                  | -40   |       |

|                 |                                           |                                                                                | RAM <sub>0, 3</sub> , Q <sub>0, 3</sub>                              |                                                      | -15  |                  | -40   |       |

| 'cc             | Power Supply Current                      | V <sub>CC</sub> = MAX.                                                         | Military<br>Commercial                                               |                                                      |      | 185              | 280   | mA    |

Notes: 1. For conditions shown as MIN. or MAX., use the appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

4. These are three-state outputs internally connected to TTL inputs. Input characteristics are measured with I<sub>678</sub> in a state such that the three-state output is OFF.

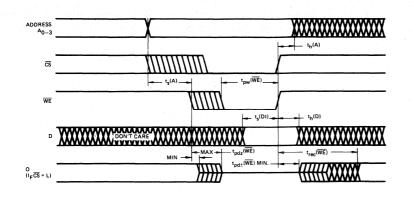

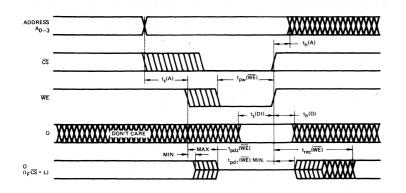

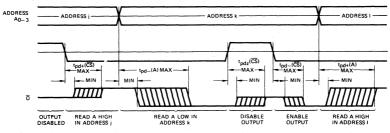

## GUARANTEED OPERATING CONDITIONS OVER TEMPERATURE AND VOLTAGE

Tables I, II, and III below define the timing requirements of the Am2901 in a system. The Am2901 is guaranteed to function correctly over the operating range when used within the delay and set-up time constraints of these tables for the appropriate device type. The tables are divided into three types of parameters; clock characteristics, combinational delays from inputs to outputs, and set-up and hold time requirements. The latter table defines the time prior to the end of the cycle (i.e., clock LOW-to-HIGH transition) that each input must be stable to guarantee that the correct data is written into one of the internal registers.

The performance of the Am2901 within the limits of these tables is guaranteed by the testing defined as "Group A, Subgroup 9" Electrical Testing. For a copy of the tests and limits used for subgroup 9, contact Advanced Micro Devices' Product Marketing.

#### **TABLE I**

#### CYCLE TIME AND CLOCK CHARACTERISTICS

| TIME                                                                                     | Am2901DC,PC | Am2901DM, FM |

|------------------------------------------------------------------------------------------|-------------|--------------|

| Read-Modify-Write Cycle<br>(time from selection of<br>A, B registers to end of<br>cycle) | 105 ns      | 120ns        |

| Maximum Clock Frequency to<br>Shift Q Register (50% duty<br>cycle)                       | 9.5MHz      | 8.3MHz       |

| Minimum Clock LOW Time                                                                   | 30ns        | 30 ns        |

| Minimum Clock HIGH Time                                                                  | 30 ns       | 30 ns        |

| Minimum Clock Period                                                                     | 105 ns      | 120ns        |

TABLE II MAXIMUM COMBINATIONAL PROPAGATION DELAYS (all in ns,  $C_1 \le 15 pF$ )

|                              | ,     | 4m290          | )1DC, F          | °C (0°C | C to +7 | 0°C; 5 | V ±5%                                | )    | Am2901DM, FM (-55°C to +125°C; 5 V ±10%) |    |                  |      |            |     |                                      |                |

|------------------------------|-------|----------------|------------------|---------|---------|--------|--------------------------------------|------|------------------------------------------|----|------------------|------|------------|-----|--------------------------------------|----------------|

| To<br>Output                 | v     | F <sub>3</sub> |                  | G, P    | F=0     | OVB    | Sh<br>Out                            | 77.7 | _                                        | _  |                  | G, ₽ | F=0        |     | Sh<br>Out                            |                |

| Input                        | τ     | г3             | C <sub>n+4</sub> | G, P    | 470     | OVR    | RAM <sub>0</sub><br>RAM <sub>3</sub> |      | <b>Y</b>                                 | F3 | C <sub>n+4</sub> | G, F | RL=<br>470 | OVR | RAM <sub>0</sub><br>RAM <sub>3</sub> | Ω <sub>0</sub> |

| A, B                         | 110   | 85             | 80               | 80      | 110     | 75     | 110                                  | -    | 120                                      | 95 | 90               | 90   | 120        | 85  | 120                                  | _              |

| D (arithmetic mode)          | 100   | 70             | 70               | 70      | 100     | 60     | 95                                   | _    | 110                                      | 80 | 75               | 75   | 110        | 65  | 105                                  | _              |

| D (I = X37) (Note 5)         | 60    | 50             | _                | _       | 60      | _      | 60                                   | -    | 65                                       | 55 | _                | -    | 65         | _   | 65                                   | _              |

| Cn                           | 55    | 35             | 30               | _       | 50      | 40     | 55                                   | _    | 60                                       | 40 | 30               | _    | 55         | 45  | 60                                   | _              |

| 1012                         | 85    | 65             | 65               | 65      | 80      | 65     | 80                                   | _    | 90                                       | 70 | 70               | 70   | 85         | 70  | 85                                   | _              |

| 1345                         | 70    | 55             | 60               | 60      | 70      | 60     | 65                                   | _    | 75                                       | 60 | 65               | 65   | 75         | 65  | 70                                   | _              |

| l <sub>678</sub>             | 55    | _              | _                | _       | _       | -      | 45                                   | 45   | 60                                       | _  | -                | _    | _          | _   | 50                                   | 50             |

| OE Enable/Disable            | 40/25 | _              | _                | _       | _       | _      |                                      | _    | 40/25                                    | _  | _                | _    | _          |     | _                                    | _              |

| A bypassing<br>ALU (I = 2xx) | 60    | <del>-</del>   | -                | -       | _       | _      | -                                    | -    | 65                                       | _  | _                | -    | -          | _   | <del>-</del>                         | - ·            |

| Clock _ (Note 6)             | 115   | 85             | 100              | 100     | 110     | 95     | 105                                  | 60   | 125                                      | 95 | 110              | 110  | 120        | 105 | 115                                  | 65             |

#### SET-UP AND HOLD TIMES (all in ns) (Note 1)

#### **TABLE III**

| From Input                               | Notes        | Am2901DC,PC (0°C              | c to +70°C, 5V ±5%) | Am2901DM, FM (-55°            | °C to +125°C, 5V ±10%) |

|------------------------------------------|--------------|-------------------------------|---------------------|-------------------------------|------------------------|

| 1 Tolli Ilipat                           | 140163       | Set-Up Time                   | Hold Time           | Set-Up Time                   | Hold Time              |

| A, B<br>Source                           | 2, 4<br>3, 5 | 105<br>t <sub>pw</sub> L + 30 | 0                   | 120<br>t <sub>pw</sub> L + 30 | 0                      |

| B Dest.                                  | 2,4          | t <sub>pw</sub> L + 15        | 0                   | t <sub>pw</sub> L +15         | 0                      |

| D (arithmetic mode)                      |              | 100                           | 0                   | 110                           | 0                      |

| D (I = X37) (Note 5)                     |              | 60                            | Ő                   | 65                            | 0                      |

| C <sub>n</sub>                           |              | 55                            | 0                   | 60                            | 0                      |

| l <sub>012</sub>                         |              | 85                            | 0                   | 90                            | . 0                    |

| l <sub>345</sub>                         |              | 70                            | 0                   | 75                            | 0                      |

| I <sub>678</sub>                         | 4            | t <sub>pw</sub> L + 15        | 0                   | t <sub>pw</sub> L + 15        | 0                      |

| RAM <sub>0</sub> , 3, Q <sub>0</sub> , 3 |              | 30                            | 0                   | 30                            | 0                      |

Notes: 1. See Figure 11 and 12.

- 2. If the B address is used as a source operand, allow for the "A, B source" set-up time; if it is used only for the destination address, use the "B dest." set-up time.

- 3. Where two numbers are shown, both must be met.

- 4. "tpwL" is the clock LOW time.

- 5.  $D\sqrt{0}$  is the fastest way to load the RAM from the D inputs. This function is obtained with I = 337.

- 6. Using Q register as source operand in arithmetic mode. Clock is not normally in critical speed path when Q is not a source.

#### SET-UP AND HOLD TIMES (minimum cycles from each input)

Set-up and hold times are defined relative to the clock LOW-to-HIGH edge. Inputs must be steady at all times from the set-up time prior to the clock until the hold time after the clock. The set-up times allow sufficient time to perform the correct operation on the correct data so that the correct ALU data can be written into one of the registers.

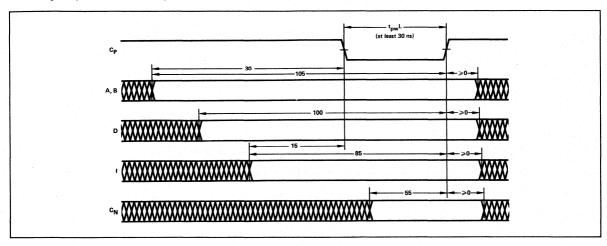

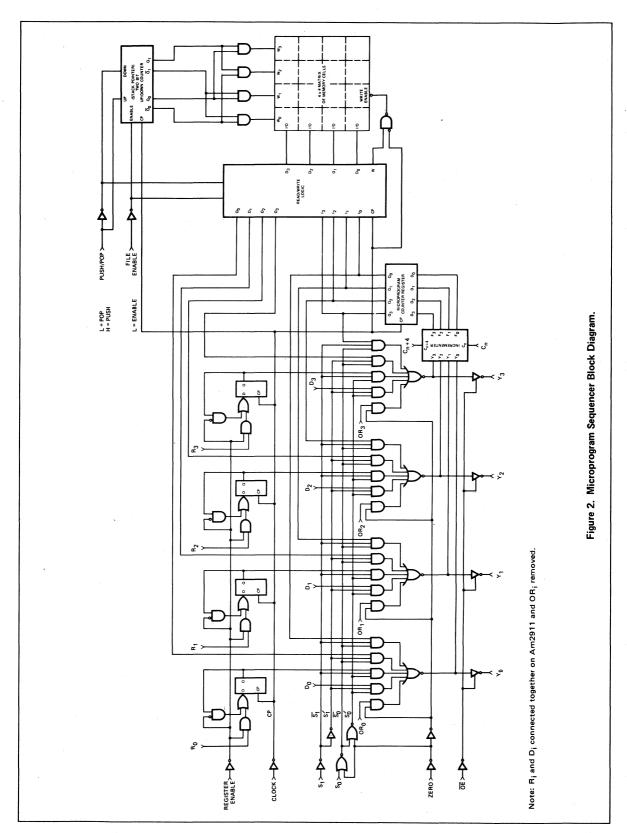

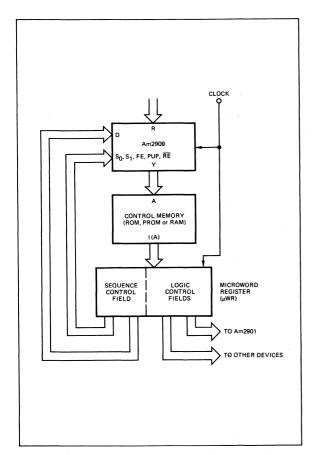

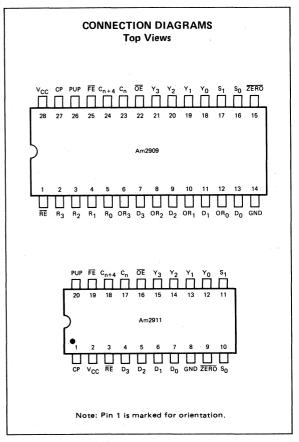

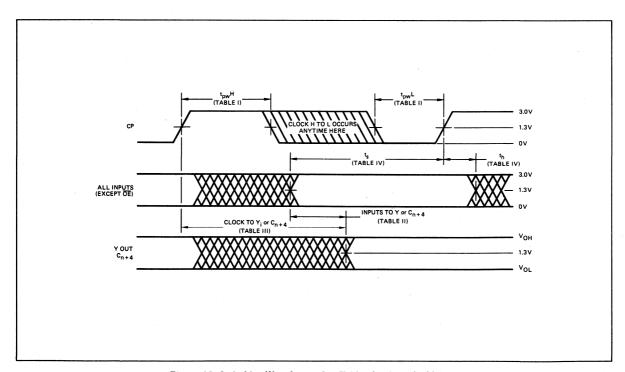

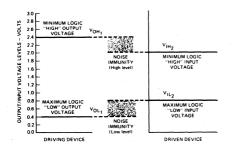

Figure 11. Minimum Cycle Times from Inputs. Numbers Shown are Minimum Data Stable Times for Am2901 DC, in ns. See Table III for Detailed Information.